UG-RISCV-SAPPHIRE-v6.0 December 2023 www.elitestek.com

### **Contents**

| Introduction                                                             |    |

|--------------------------------------------------------------------------|----|

| VexRiscy RISC-V Core                                                     |    |

| Efinity® RISC-V Embedded Software IDE                                    |    |

| Required Software                                                        |    |

| Required Hardware                                                        |    |

| Chapter 1: Install Software and SoC                                      | 8  |

| Install the Efinity Software                                             | 8  |

| Install the Efinity RISC-V Embedded Software IDE                         | 8  |

| Chapter 2: IP Manager                                                    | c  |

| Customizing the Sapphire SoC                                             |    |

| SoC Configuration Guideline                                              |    |

| Modify the Bootloader                                                    |    |

| Updating Bootloader with Efinity BRAM Initial Content Updater            |    |

| Chapter 3: Program the Board with the Sapphire RTL Design                | 24 |

| About the Example Design                                                 |    |

| Enable the On-Board 10 MHz Oscillator (T120 BGA324 Board)                |    |

| Enable the LPDDR4x Memory (Ti180 J484 Board)                             |    |

| Installing USB Drivers                                                   | 26 |

| Program the Development Board                                            | 28 |

| Chapter 4: Simulate                                                      | 20 |

| •                                                                        |    |

| Chapter 5: Launch Efinity RISC-V Embedded Software IDE                   |    |

| Sapphire SoC IDE Backward Compatibility                                  |    |

| Launching the Efinity RISC-V Embedded Software IDE Optimization Settings |    |

| Optimization settings                                                    |    |

| Chapter 6: Create, Import, and Build a Software Project                  | 35 |

| Create a New Project                                                     |    |

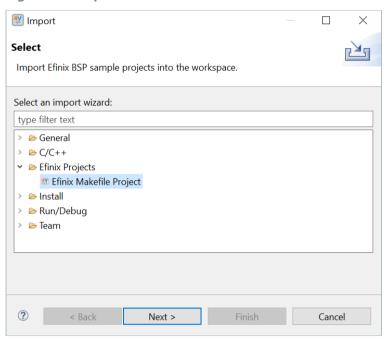

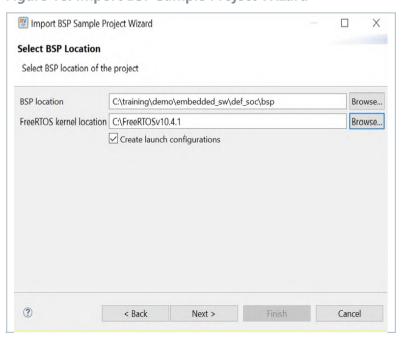

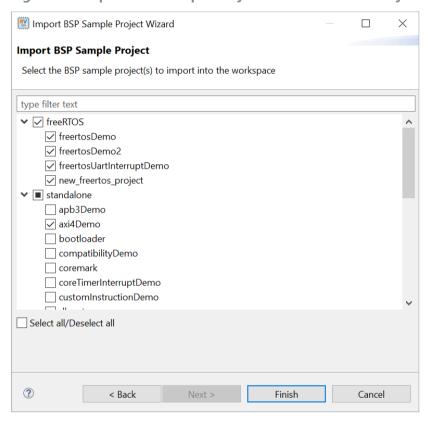

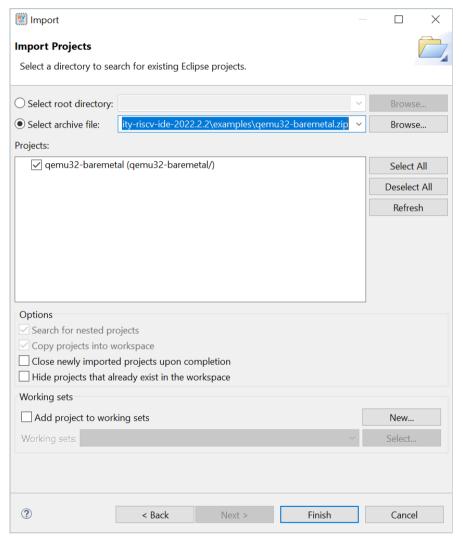

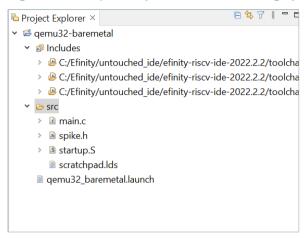

| Import Sample Projects                                                   |    |

| Build                                                                    | 41 |

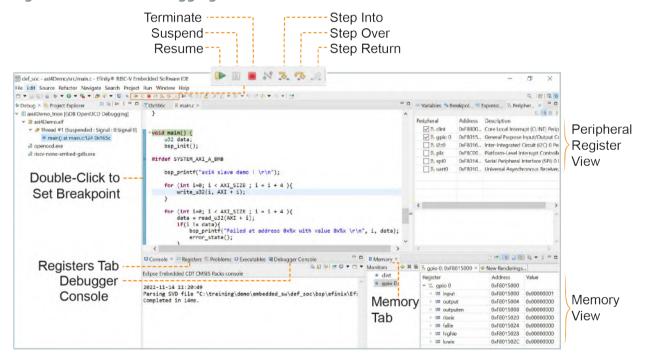

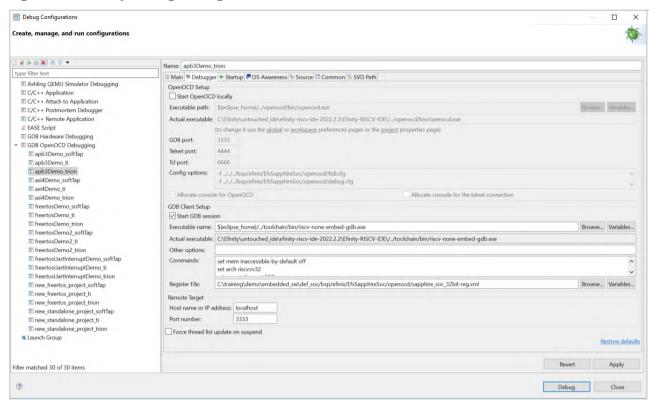

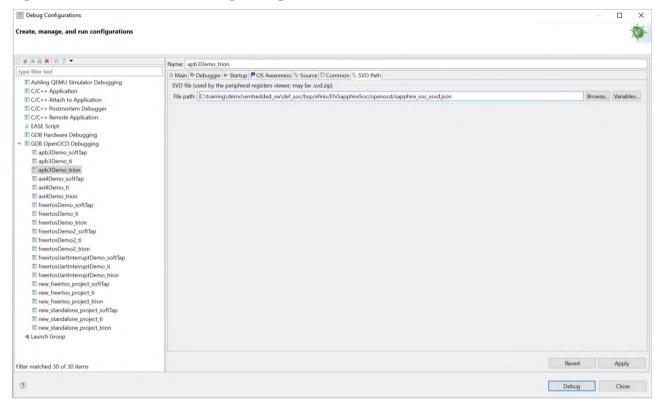

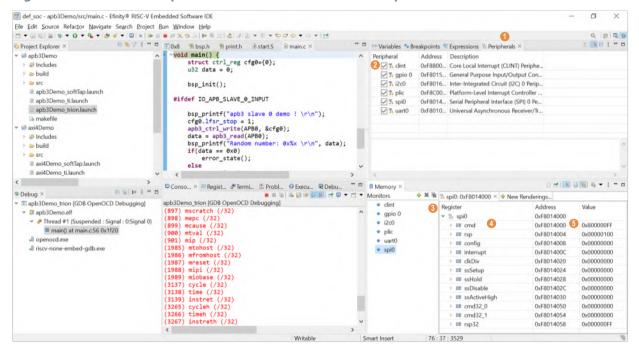

| Chapter 7: Debug with the OpenOCD Debugger                               | 42 |

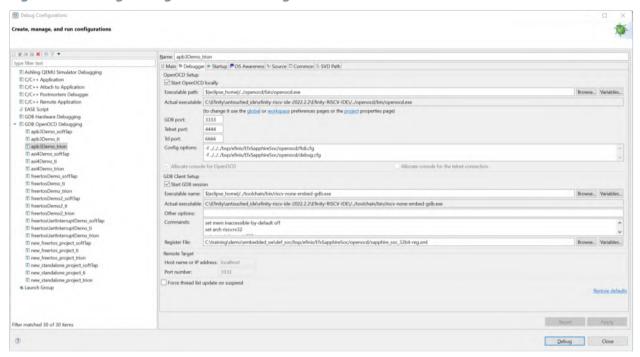

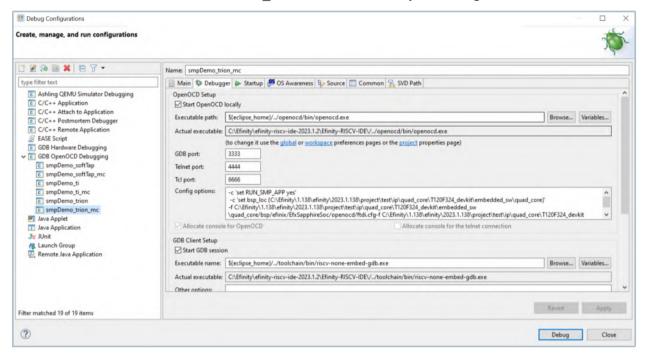

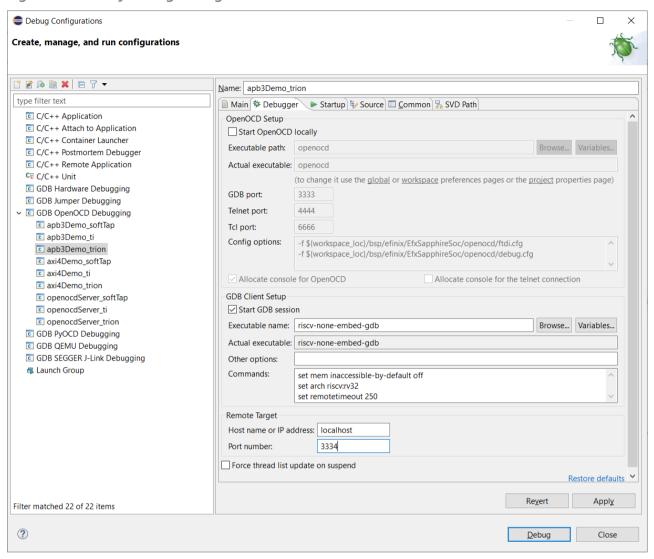

| Launch the Debug Script                                                  | 43 |

| Debug                                                                    |    |

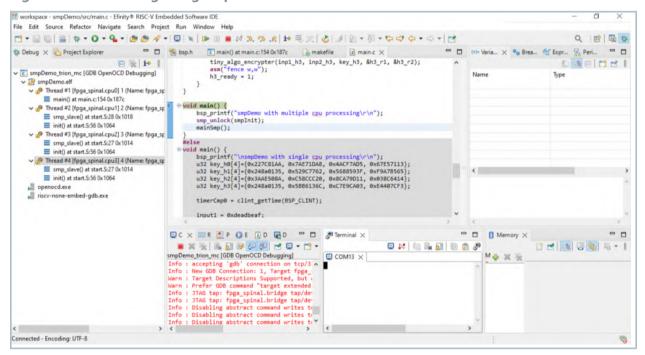

| Debug - Multiple Cores                                                   | 45 |

| Debug - Single Core                                                      |    |

| Debug - SMP                                                              |    |

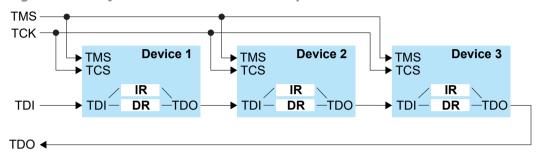

| Debug - Daisy Chain                                                      |    |

| Peripheral Register View                                                 |    |

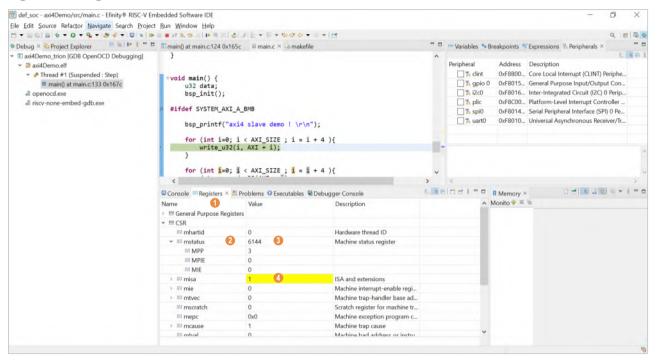

| CSR Register View                                                        |    |

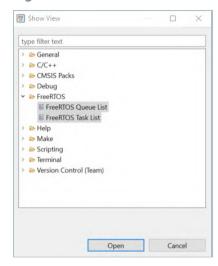

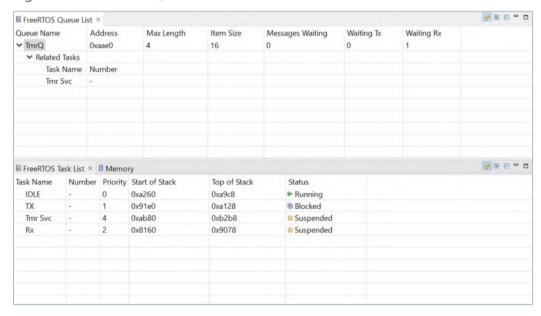

| FreeRTOS View                                                            |    |

| QEMU Emulator                                                            | 50 |

| Chapter 8: Boot Sequence                                                 |    |

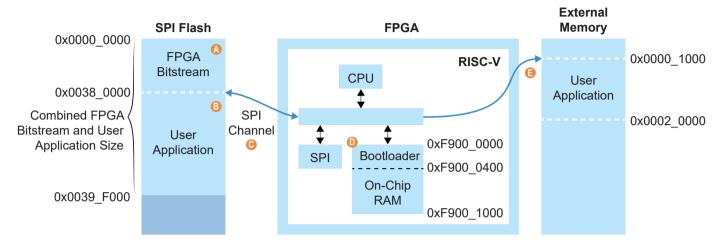

| Boot Sequence: Case A                                                    |    |

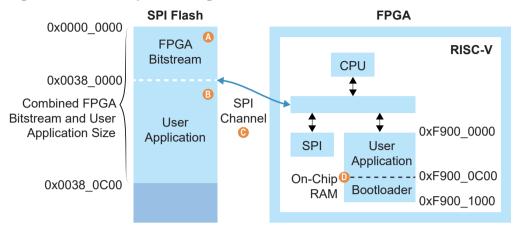

| Boot Sequence: Case B                                                    |    |

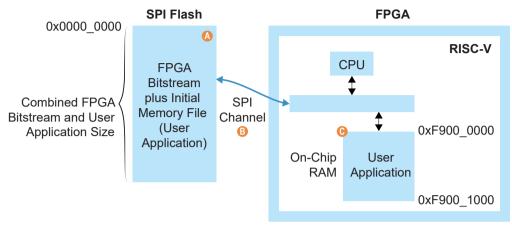

| Boot Sequence: Case C                                                    |    |

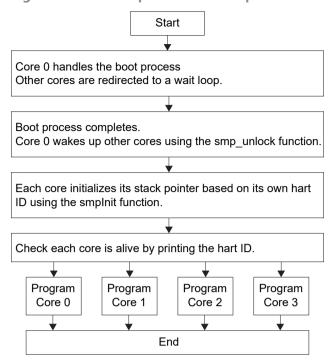

| Booting Multiple Cores                                                   | 62 |

| Chapter 9: Create Your Own RTL Design                                    |    |

| Target another FPGA                                                      | 64 |

| Target another 易灵思 Board                                                 |    |

| Target Your Own Board                                                    |    |

| Create a Custom AXI4 Slave Peripheral                                    |    |

| Create a Custom APB3 Peripheral                                          | 68 |

| Use another DDR DRAM Module (Trion Only)                    |     |

|-------------------------------------------------------------|-----|

| Use the I <sup>2</sup> C Interface for DDR Calibration      |     |

| Remove Unused Peripherals from the RTL Design               | 69  |

| Chapter 10: Create Your Own Software                        |     |

| Deploying an Application Binary                             |     |

| Boot from a Flash Device                                    |     |

| Boot from the OpenOCD Debugger                              |     |

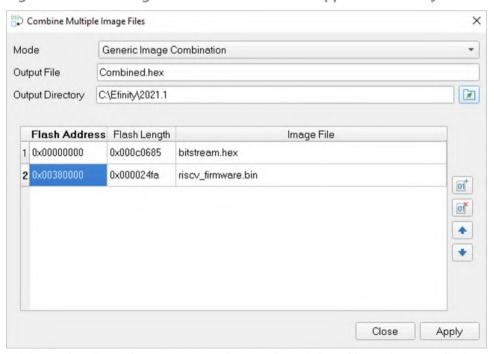

| Copy a User Binary to Flash (Efinity Programmer)            |     |

| About the Board Specific Package                            |     |

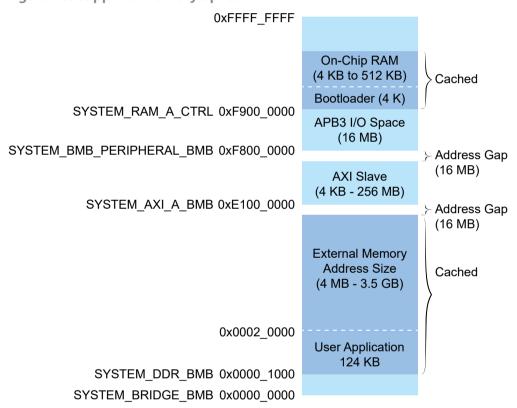

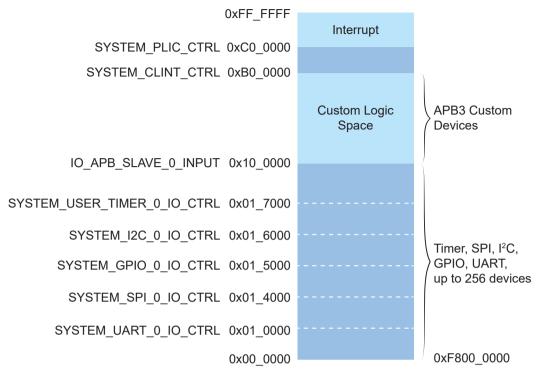

| Address Map                                                 |     |

| Example Software                                            |     |

| Axi4Demo Design                                             |     |

| apb3Demo                                                    |     |

| compatibilityDemo                                           |     |

| coreTimerInterruptDemo                                      |     |

| coremark                                                    |     |

| customInstructionDemo                                       |     |

| dCacheFlushDemo                                             |     |

| dhrystone Example                                           |     |

| FreeRTOS Examples                                           |     |

| freertosUartInterruptDemo Example                           |     |

| fpuDemo                                                     |     |

| gpioDemo                                                    |     |

| iCacheFlushDemo                                             |     |

| inlineAsmDemo                                               |     |

| i2cDemo Example                                             |     |

| i2cEepromDemo                                               |     |

| i2cMasterDemo Design                                        |     |

| i2cSlaveDemo Design                                         |     |

| memTest Example                                             |     |

| nestedInterruptDemo                                         |     |

| openocdServer                                               |     |

| semihostingDemo                                             |     |

| smpDemo                                                     |     |

| spiDemo Example                                             |     |

| spiReadFlashDemo Example                                    |     |

| spiWriteFlashDemo Example                                   |     |

| uartEchoDemo                                                |     |

| UartInterruptDemo Example                                   |     |

| userInterruptDemo Example                                   |     |

| user Timer Demo                                             | 95  |

| Chapter 11: Third-party Debugger                            | 96  |

| Chapter 12: Using a UART Module                             | 97  |

| Using the On-board UART (钛金系列)                              |     |

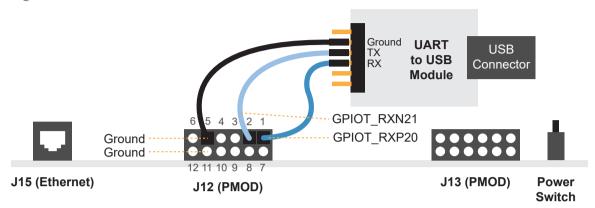

| Set Up a USB-to-UART Module (Trion)                         |     |

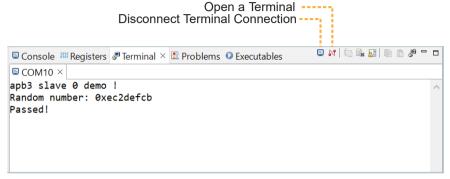

| Open a Terminal                                             |     |

| Enable Telnet on Windows                                    |     |

|                                                             |     |

| Chapter 13: Unified Printf                                  |     |

| Bsp_print                                                   |     |

| Bsp_printf                                                  |     |

| Bsp_printf_full                                             |     |

| Semihosting Printing                                        |     |

| Preprocessor Directives                                     | 104 |

| Chapter 14: Using a Soft JTAG Core for Example Designs      | 105 |

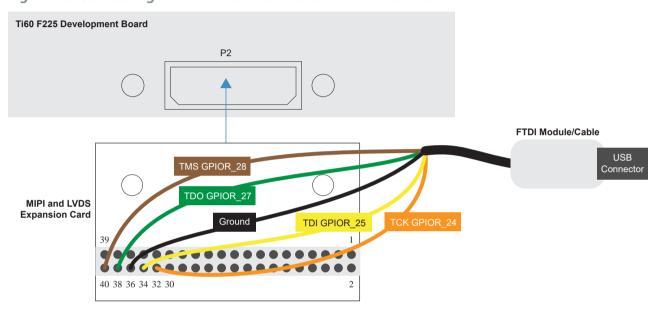

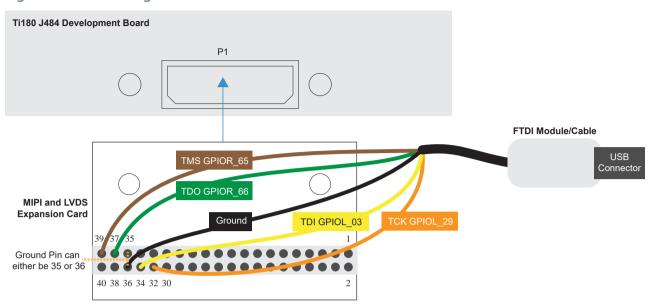

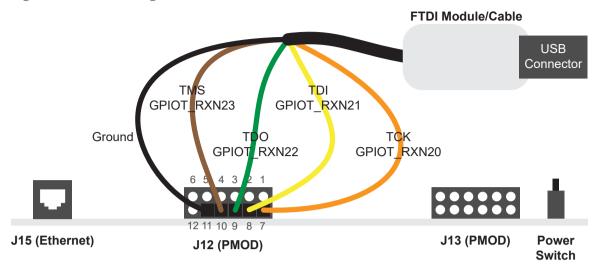

| Connect the FTDI Mini-Module                                | 106 |

|                                                             |     |

| Chapter 15: Migrating to the Sapphire SoC                   |     |

| IVIIGIALITY TO THE SANDTHE SOC VA.O HOTH A FIEVIOUS VEISIOH |     |

| 111        |

|------------|

| 118        |

| 119        |

| 119        |

| 120        |

| 122        |

| 122        |

| 122        |

| 123        |

| دے۱<br>122 |

| 123        |

| 123        |

| 124        |

| 124        |

| 125        |

| 125        |

| 128        |

| 131        |

| 140        |

| 142        |

| 143        |

| 144        |

| 146        |

| 148        |

| 152        |

| 154        |

| 155        |

| 158        |

|            |

| 158        |

| 159        |

| 160        |

| 164        |

| 167        |

| 168        |

| 168        |

| 169        |

| 170        |

| 171        |

| 171        |

| 171        |

| 172        |

| 172        |

| 173        |

| 173        |

| 174        |

| 175        |

| 177        |

| 178        |

| 179        |

| 181        |

|            |

### Introduction

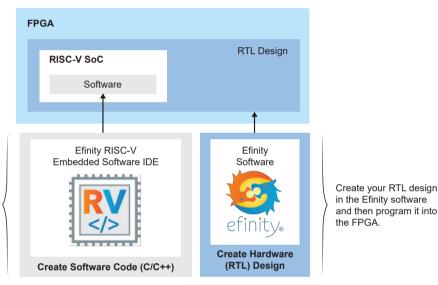

易灵思 provides a soft configurable RISC-V SoC, called Sapphire, that you can implement in Trion® or 钛金系列 FPGAs. This user guide describes how to:

- Build RTL designs using the Sapphire RISC-V SoC using an example design targeting an 易灵思® development board, and how to extend the example for your own application.

- Set up the software development environment using an example project, create your own software based on example projects, and use the API.

**Note:** The Sapphire SoC v2.0, released with the Efinity software v2021.2, has significant improvements from previous versions, and you cannot migrate an existing design to it automatically. 易灵思 recommends that you use v2.0 or higher for all new designs. You can continue to use previous versions with the Efinity software v2021.1. If you want to migrate an existing design to v2.0, refer to **Migrating to the Sapphire SoC v2.0 from a Previous Version** on page 109.

Figure 1: Designing Hardware and Software for the Sapphire RISC-V SoC

Write your C/C++ code using our Efinity RISC-V Embedded software IDE, then copy it to the flash memory.

Learn more: Refer to the Sapphire RISC-V SoC Data Sheet for detailed specifications on the SoC.

### VexRiscv RISC-V Core

The Sapphire SoC is based on the VexRiscv core created by Charles Papon. The VexRiscv core is a 32-bit CPU using the ISA RISCV32I with M, A, F, D, and C extensions, has six pipeline stages (fetch, injector, decode, execute, memory, and writeback), and a configurable feature set.

In the Sapphire SoC, the VexRiscv core is user configurable, and can support AXI4 and APB3 bus interfaces and instruction and data caches. The Sapphire SoC VexRiscv core uses Little-Endian for its memory storage.

The VexRiscv core won first place in the RISC-V SoftCPU contest in 2018. (1)

<sup>(1)</sup> https://www.businesswire.com/news/home/20181206005747/en/RISC-V-SoftCPU-Contest-Winners-Demonstrate-Cutting-Edge-RISC-V

### Efinity® RISC-V Embedded Software IDE

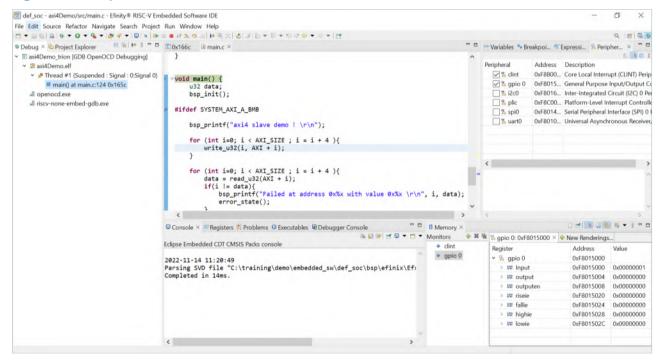

The Efinity® RISC-V Embedded Software IDE is an Eclipse-based Integrated Development Environment (IDE) powered by Ashling's **RiscFree™** IDE for Sapphire SoC. It provides a complete and seamless environment for RISC-V C and C++ software development.

#### Features include:

- Eclipse based IDE with full source project creation, edit, build, and debug

- QEMU emulator support for 32-bit RISC-V cores with out-of-box example design

- · High-level Peripheral Register viewer

- Control and Status Register (CSR) viewer

- Integrated new project creation process with Board Support Package (BSP) generated in the Efinity software

- Integrated example program import process with Board Support Package (BSP) generated in the Efinity software

- Integrated serial terminal for viewing UART data

- FreeRTOS task and queue list debug view

- Debug support for all OpenOCD compliant probes

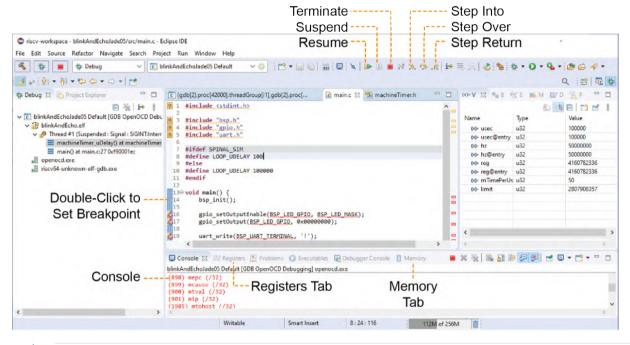

Figure 2: Efinity RISC-V Embedded Software IDE

### **Required Software**

To write software for the Sapphire SoC, you need the following tools. The Efinity RISC-V Embedded Software IDE installer for Windows and Linux operating systems are available in the Efinity software download page.

#### Efinity® Software

易灵思<sup>®</sup> development environment for creating RTL designs targeting Trion<sup>®</sup> or 钛金系列 FPGAs. The software provides a complete RTL-to-bitstream flow, simple, easy to use GUI interface, and command-line scripting support.

Version: 2021.1 or higher

#### Efinity RISC-V Embedded Software IDE

The Efinity RISC-V Embedded Software IDE is an Eclipse-based Integrated Development Environment (IDE) powered by Ashling's **RiscFree™** IDE for Sapphire SoC and provides a complete provides a complete, seamless environment for RISC-V C and C++ software development. The RISC-V IDE includes the following packages:

Disk space required: 2.4 GB (Windows), 2.5 GB (Linux)

**xPack GNU RISC-V Embedded GCC**—Open-source, prebuilt toolchain from the xPack Project.

Version: 8.3.0-2.3

Disk space required: 1.53 GB (Windows), 1.5 GB (Linux)

**OpenOCD Debugger**—The open-source Open On-Chip Debugger (OpenOCD) software includes configuration files for many debug adapters, chips, and boards. Many versions of OpenOCD are available. The 易灵思 RISC-V flow requires a custom version of OpenOCD that includes the VexRiscv 32-bit RISC-V processor.

Version: 0.11.0 (20230502)

Disk space required: 17.4 MB (Windows), 16.3 MB (Linux)

**Note:** 易灵思 recommends you use the latest version of Efinity RISC-V Embedded Software IDE to ensure compatibility with Efinity software.

### Required Hardware

- Trion® T120 BGA324 Development Board, 钛金系列 Ti60 F225 Development Board, or 钛金系列 Ti180 J484 Development Board

- 5 or 12 V power cable

- Micro-USB cable

- Computer or laptop

- (Optional) USB to UART converter module for the <sup>(2)</sup>

- Trion® T120 BGA324 Development Board<sup>(3)</sup>

- (Optional) FTDI mini-module or FTDI chip cable, C232HM-DDHSL-0, if you want to use the OpenOCD debugger and Efinity® Debugger simultaneously

Note: Some of the software examples provided with the SoC use a UART terminal to display messages. See **Set Up a USB-to-UART Module (Trion)** on page 98 and **Using the On-board UART (钛金系列)** on page 97 for more information.

<sup>(3)</sup> The 钛金系列 Ti60 F225 Development Board has an on-board USB-to-UART converter and does not require a separate module.

(3) The 钛金系列 Ti60 F225 Development Board and 钛金系列 Ti180 J484 Development Board have an on-board USB-to-UART converter and do not require a separate module.

### Install Software and SoC

#### **Contents:**

- Install the Efinity Software

- Install the Efinity RISC-V Embedded Software IDE

### Install the Efinity Software

If you have not already done so, download the Efinity software from the Support Center and install it. For installation instructions, refer to the Efinity Software Installation User Guide.

Warning: Do not use spaces or non-English characters in the Efinity path.

### Install the Efinity RISC-V Embedded Software IDE

Download the installer file in **Efinity RISC-V Embedded Software IDE <version>** from the Support Center.

To install the Efinity RISC-V Embedded Software IDE:

#### Windows

- 1. Execute the installer file **efinity-riscv-ide-<version>-windows-x64.exe** to launch the installer.

- **2.** Follow the steps in the setup process.

- 3. Install Efinity RISC-V IDE in a preferred directory or use the default directory c:\Efinity\efinity-riscv-ide-<version>\. Example, c:\Efinity\efinity-riscv-ide-2022.2.3\.

#### Linux

Execute the installer file efinity-riscv-ide-<version>-linux-x64.run or run the installer using ./<installer run file>. Run the executable script with command:

chmod +x <installer run file>

- 2. Select either to install the RISC-V IDE for the current user or multiple users.

- 3. Follow the steps in the setup wizard.

- 4. Install Efinity RISC-V IDE in a preferred directory or use the default directory /home/user/efinity/efinity-riscv-ide-<version>. Example, /home/user/efinity/efinity-riscv-ide-2022.2.3/.

#### Note:

- 易灵思 provides FREE licences for the Efinity software. Alternatively, when you buy a development kit, you also get a software license and one year of upgrades. After the first year, you can request a free maintenance renewal. The Efinity software is available for download from the Support Center. To get your free license, create an account, login, and then go to the Efinity page to request your license.

- 易灵思 recommends you use the latest version of Efinity RISC-V Embedded Software IDE to ensure compatibility with Efinity software.

### **IP** Manager

#### **Contents:**

- Customizing the Sapphire SoC

- SoC Configuration Guideline

- Modify the Bootloader

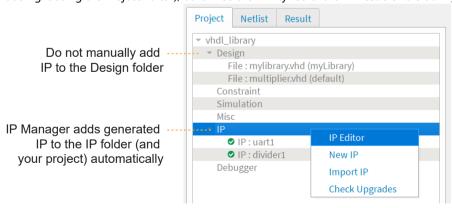

The Efinity® IP Manager is an interactive wizard that helps you customize and generate 易灵思® IP cores. The IP Manager performs validation checks on the parameters you set to ensure that your selections are valid. When you generate the IP core, you can optionally generate an example design targeting an 易灵思 development board and/or a testbench. This wizard is helpful in situations in which you use several IP cores, multiple instances of an IP core with different parameters, or the same IP core for different projects.

The IP Manager consists of:

- IP Catalog—Provides a catalog of IP cores you can select. Open the IP Catalog using the toolbar button or using **Tools** > **Open IP Catalog**.

- IP Configuration—Wizard to customize IP core parameters, select IP core deliverables, review the IP core settings, and generate the custom variation.

- IP Editor—Helps you manage IP, add IP, and import IP into your project.

#### Generating Sapphire SoC with the IP Manager

The following steps explain how to customize an IP core with the IP Configuration wizard.

- 1. Open the IP Catalog.

- 2. Choose an IP core and click **Next**. The **IP Configuration** wizard opens.

- 3. Enter the module name in the Module Name box.

**Note:** You cannot generate the core without a module name.

- **4.** Customize the IP core using the options shown in the wizard. For detailed information on the options, refer to the IP core's user guide or on-line help.

- **5.** (Optional) In the **Deliverables** tab, specify whether to generate an IP core example design targeting an 易灵思<sup>®</sup> development board and/or testbench. For SoCs, you can also optionally generate embedded software example code. These options are turned on by default.

- **6.** (Optional) In the **Summary** tab, review your selections.

- 7. Click **Generate** to generate the IP core and other selected deliverables.

- **8.** In the **Review configuration generation** dialog box, click **Generate**. The Console in the **Summary** tab shows the generation status.

**Note:** You can disable the **Review configuration generation** dialog box by turning off the **Show Confirmation Box** option in the wizard.

**9.** When generation finishes, the wizard displays the **Generation Success** dialog box. Click **OK** to close the wizard.

The wizard adds the IP to your project and displays it under **IP** in the Project pane.

#### Generated RTL Files

The IP Manager generates these files and directories:

- <module name> define.vh—Contains the customized parameters.

- <module name> tmpl.v—Verilog HDL instantiation template.

- <module name> tmpl.vhd—VHDL instantiation template.

- <module name>.v—IP source code.

- settings.json—Configuration file.

- <kit name>\_devkit—Has generated RTL, example design, and Efinity® project targeting a specific development board.

- Testbench—Contains generated RTL and testbench files.

**Note:** Refer to the IP Manager chapter of the Efinity Software User Guide for more information about the Efinity IP Manager.

#### **Generated Software Code**

If you choose to output embedded software, the IP Manager saves it into the ct>/

embedded sw/<SoC module> directory.

- bsp—Board specific package.

- **config**—Has the Eclipse project settings file and OpenOCD debug configuration settings files for Windows.

- config\_linux—Has the Eclipse project settings file and OpenOCD debug configuration settings files for Linux.

- software—Software examples.

- tool—Helper scripts.

- **cpu<n>.yaml**—CPU file for debugging where <n> is the core number, up to 4 cores.

#### Instantiating the SoC

The IP Manager creates these template files in the roject>/ip/<module name> directory:

- <module name>.v\_tmpl.v is the Verilog HDL module.

- <module name>.v\_tmpl.vhd is the VHDL component declaration and instantiation template.

To use the IP, copy and paste the code from the template file into your design and update the signal names to instantiate the IP.

**Important:** When you generate the IP, the software automatically adds the module file (<module name>.v) to your project and lists it in the IP folder in the Project pane. Do not add the <module name>.v file manually (for example, by adding it using the Project Editor); otherwise the Efinity® software will issue errors during compilation.

### Customizing the Sapphire SoC

There are two options available for the Sapphire SoC, which provides for different needs and applications:

- **Standard**—Best performance. This option utilizes more area of resources to achieve the best performance. Advanced features are only available in this option.

- **Lite**—Smallest area. This option utilizes a small area of resources by limiting the Sapphire SoC performance. Advanced features are not available in this option.

You customize the Sapphire SoC using the IP Configuration wizard. The parameters are arranged on tabs so you can click through them more easily.

There will be differences in the **SOC** and **Cache/Memory** tabs depending on the chosen option, either **Standard** or **Lite**, but all the other tabs are the same across both options.

**Table 1: Sapphire SoC Tab Parameters**

| Parameter                           | Options           | Description                                                                                                                                          | Availability         |

|-------------------------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| Option                              | Standard,<br>Lite | This option in the Sapphire SoC provides for different applications. Default: Standard                                                               | Standard and<br>Lite |

| Core Number                         | 1 - 4             | Enter the number of CPU cores. Default: 1                                                                                                            | Standard only        |

| Frequency (MHz)                     | 20 - 400          | Enter the frequency in MHz. Default: 100                                                                                                             | Standard and Lite    |

| Peripheral Clock                    | On, off           | Choose whether you want to run a dedicated clock for the APB3 slaves (SPI, I2C, GPIO, UART, and user timer) and AXI4 slave.                          | Standard and Lite    |

| Peripheral Clock<br>Frequency (MHz) | 20 - 200          | Enter the peripheral clock frequency in MHz.                                                                                                         | Standard and Lite    |

| Cache                               | On, off           | Choose whether you want to include I\$ and D\$ caches.                                                                                               | Standard and Lite    |

| Custom Instruction                  | On, off           | Choose whether to enable the custom instruction interface.                                                                                           | Standard only        |

| Linux Memory<br>Management Unit     | On, off           | Choose whether to enable the Linux MMU.                                                                                                              | Standard only        |

| Floating-point Unit                 | On, off           | Choose whether to enable the FPU.                                                                                                                    | Standard only        |

| Atomic Extension                    | On, off           | Choose whether to enable atomic extension instruction support.                                                                                       | Standard only        |

|                                     |                   | If you enable the Linux MMU, this option must be enabled and is turned on by default.                                                                |                      |

| Compressed<br>Extension             | On, off           | Choose whether to enable compressed instruction support.                                                                                             | Standard only        |

| Multiplication and<br>Division      | On, off           | Choose whether to enable multiplication and division, which is the RISC-V M extension.                                                               | Lite only            |

|                                     |                   | Note: This feature is turned on in Standard option.                                                                                                  |                      |

| Barrel Shifter                      | On, off           | Choose whether to include the barrel shifter, which is a module that can perform shift operations on any number of bits within a single clock cycle. | Lite only            |

|                                     |                   | Note: This feature is turned on in Standard option.                                                                                                  |                      |

| CSR Optimization                    | On, off           | Choose whether to minimize the number of RISC-V Control and Status Registers.                                                                        | Lite only            |

|                                     |                   | Note: This feature is turned off when the RISC-V standard debug interface is enabled. This feature is also turned off in Standard option.            |                      |

**Important:** When running the SoC at high frequencies, 易灵思 recommends that you use the TIMING\_1 place and route optimization. To set this option:

- 1. Open the Project Editor.

- 2. Click the Place and Route tab.

- 3. Double-click the Value cell for --optimization\_level.

- 4. Choose TIMING\_1.

- 5. Click **OK** and then compile.

**Table 2: Sapphire Cache/Memory Tab Parameters**

| Parameter                            | Options                                                                                                                                 | Description                                                                                                                                                  | Availability      |

|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| Data Cache Way                       | 1, 2, 4, 8                                                                                                                              | Choose the number of ways for the data cache. Default: 1                                                                                                     | Standard and Lite |

| Cache Size                           | 1 KB, 2 KB, 4 KB,<br>8 KB, 16 KB, 32 KB                                                                                                 | Choose the size of the data cache. Default: 4 KB                                                                                                             | Standard and Lite |

| Instruction Cache<br>Way             | 1, 2, 4, 8                                                                                                                              | Choose the number of ways for the instruction cache. Default: 1                                                                                              | Standard and Lite |

| Cache Size                           | 1 KB, 2 KB, 4 KB,<br>8 KB, 16 KB, 32 KB                                                                                                 | Choose the size of the instruction cache. Default: 4 KB                                                                                                      | Standard and Lite |

| External Memory<br>Interface         | On, off                                                                                                                                 | On: By default. Instantiate the external memory interface. Off: Do not use the external memory interface.                                                    | Standard and Lite |

| AXI Interface Type                   | On, off                                                                                                                                 | On: Use an AXI4 full duplex interface. Off: By default. Use an AXI3 half duplex interface.                                                                   | Standard and Lite |

| AXI Interface<br>Optimization        | Optimize for area,<br>Optimize for<br>bandwidth                                                                                         | Optimize for area: Smaller area but lower bandwidth. Optimize for bandwidth: Full bandwidth but uses more resources.                                         | Lite only         |

| External Memory<br>Clock Domain      | Unified System<br>Clock, Dedicated<br>Memory Clock                                                                                      | Unified System Clock: The external memory interface will use the system clock (io_systemClk). This will utilize lesser resource as no CDC logic is required. | Lite only         |

|                                      |                                                                                                                                         | Note: By sharing the system clock, the frequency of the system clock will be limited by the slowest domain in the system.                                    |                   |

|                                      |                                                                                                                                         | Dedicated Memory Clock: The external memory interface will use the dedicated memory clock (io_memoryClk). This will utilize more resource.                   |                   |

| External Memory<br>Data Width        | 32, 64, 128,<br>256, 512                                                                                                                | Choose the data width for the AXI interface. Default: 128                                                                                                    | Standard and Lite |

| External Memory<br>AXI3 Address Size | 4 MB, 8 MB, 16<br>MB, 32 MB, 64 MB,<br>128 MB, 256 MB,<br>0.5 GB, 1 GB,<br>1.5 GB, 2 GB, 2.5<br>GB, 3 GB, 3.5 GB                        | Choose the address size for the AXI interface. Default: 3.5 GB                                                                                               | Standard and Lite |

| On-Chip RAM Size                     | 1 KB, 2 KB, 4 KB, 8 KB, 16 KB, 24 KB, 32 KB, 48 KB, 64 KB, 80 KB, 96 KB, 128 KB, 144 KB, 160 KB, 192 KB, 224 KB, 256 KB, 384 KB, 512 KB | Choose the size of the internal BRAM.  Default: 4 KB                                                                                                         | Standard and Lite |

| Custom On-Chip<br>RAM Application    | On, off                                                                                                                                 | On: Overwrite the default SPI flash bootloader with the user application.  Off: By default. Use the default SPI flash bootloader.                            | Standard and Lite |

| User Application<br>Path             | -                                                                                                                                       | Enter the path to your target user application. The file must be in <b>.hex</b> format.                                                                      | Standard and Lite |

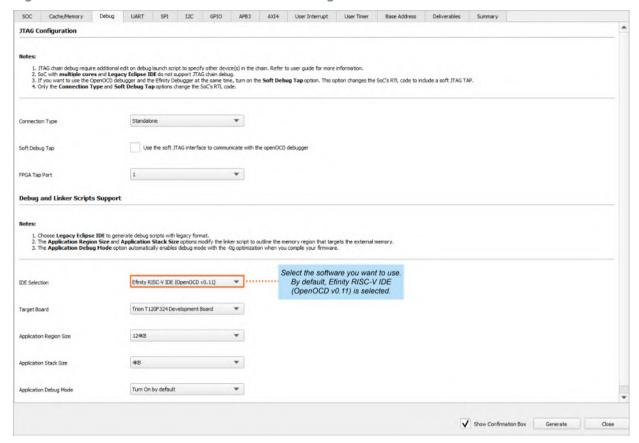

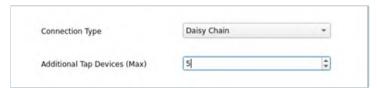

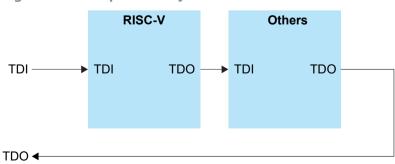

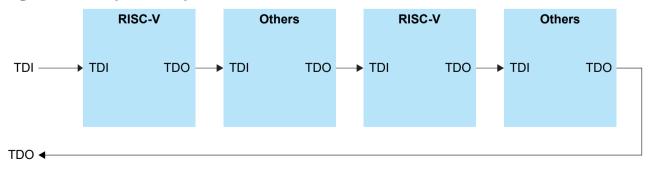

**Table 3: Sapphire Debug Tab Parameters**

| Parameter                       | Options                                                          | Description                                                                                                                                                                                       |

|---------------------------------|------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Connection Type                 | Standalone, Chain                                                | Choose whether you want to include the chain debug feature to the SoC. This allows the connection of multiple devices for JTAG debugging with a daisychain. Else, select as standalone.           |

|                                 |                                                                  | Standalone: By default. The debug feature is available for the standalone SoC only.                                                                                                               |

|                                 |                                                                  | Daisy-chain: The debug feature extends to multiple devices or SoC in the chain. Once enabled, you can debug multiple devices with a single debugger.                                              |

| RISC-V Standard<br>Debug        | On, off                                                          | Choose whether to enable the RISC-V standard debug interface.                                                                                                                                     |

|                                 |                                                                  | On: Use the debug module that follows the RISC-V External Debug Support Version 0.13.                                                                                                             |

|                                 |                                                                  | (Recommended) <sup>(4)(5)</sup>                                                                                                                                                                   |

|                                 |                                                                  | Off: Use debug module that is customized for the VexRiscv core.                                                                                                                                   |

| Hardware<br>Breakpoint          | 0 - 4                                                            | Number of hardware breakpoints. This hardware breakpoint is a program type breakpoint.                                                                                                            |

|                                 |                                                                  | Only applicable when the RISC-V Standard debug is turned on.                                                                                                                                      |

| Additional Tap<br>Devices (Max) | 1 - 8                                                            | The maximum number of extra devices in the chain. This option is only applicable when you are using daisy-chain connection type.  Default: 1                                                      |

| Soft Debug Tap                  | On, off                                                          | Choose whether you want to include a soft debug TAP for debugging.                                                                                                                                |

|                                 |                                                                  | Off: By default. The SoC uses the JTAG User TAP interface block to communicate with the OpenOCD debugger.                                                                                         |

|                                 |                                                                  | On: The SoC has a soft JTAG interface to communicate with the OpenOCD debugger. You need to use this setting if you want to use the soft JTAG interface instead of the JTAG User TAP.             |

| FPGA Tap Port                   | 1, 2, 3, 4                                                       | Choose which Tap port you want to target with the OpenOCD debugger. This option is only applicable when you are using the JTAG User Tap interface block to communicate with the OpenOCD debugger. |

| Target Board/                   | Trion T120 BGA324 Development Board                              | Choose which board you want to target with                                                                                                                                                        |

| Cable/Module                    | Trion T120 BGA576 Development Board                              | OpenOCD.                                                                                                                                                                                          |

|                                 | Trion T20 BGA256 Development Board                               | Choose <b>Custom</b> to target your own board.                                                                                                                                                    |

|                                 | Xyloni                                                           |                                                                                                                                                                                                   |

|                                 | 钛金系列 Ti60 F225 Development Board                                 |                                                                                                                                                                                                   |

|                                 | 钛金系列 Ti180 J484 Development Board                                |                                                                                                                                                                                                   |

|                                 | C232HM-DDHSL-0 (Soft debug)                                      |                                                                                                                                                                                                   |

|                                 | FTDI Module FT2232H (Soft debug) FTDI Module FT4232 (Soft debug) |                                                                                                                                                                                                   |

|                                 | ISX-DLC EF001 Programming Cable                                  |                                                                                                                                                                                                   |

|                                 | Custom                                                           |                                                                                                                                                                                                   |

| IDE Selection                   | Legacy Eclipse IDE (OpenOCD v0.10)                               | Choose which debug script format you want to                                                                                                                                                      |

|                                 | Efinity RISC-V IDE (OpenOCD v0.11)                               | generate. This selection allows you to roll back to target the Legacy Eclipse IDE. By default, Efinity RISC-V Embedded Software IDE is targeted.                                                  |

| Custom Target<br>Board          | -                                                                | Enter the name of your board.                                                                                                                                                                     |

<sup>(4)</sup> RISC-V standard debug is supported starting from Efinity 2023.1 or later. Debugging with RISC-V standard debug is only supported by Efinity RISC-V Embedded Software IDE version 2023.1 or later.

(5) The RISC-V standard debug requires connecting the hard JTAG UPDATE and RESET signals. Before Efinity 2023.1, these signals were unconnected. However, with Efinity 2023.1, the generated example designs automatically connect both signals.

| Parameter                  | Options                                                                                                      | Description                                                                                                                                                                                                                       |

|----------------------------|--------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Application<br>Region Size | 124KB, 252KB, 508KB, 1MB, 2MB, 4MB,<br>8MB, 16MB, 32MB, 64MB, 128MB, 256MB                                   | Modify the linker script to outline the region for the user application. This option is only applicable for SoCs with external memory. For SoCs with internal memory, the region size is determined by the onchip RAM size.       |

| Application<br>Stack Size  | 1KB, 2KB, 4KB, 8KB, 16KB, 32KB, 64KB,<br>128KB, 256KB, 512KB, 1MB, 2MB, 4MB,<br>8MB, 16MB, 32MB, 64MB, 128MB | Modify the linker script to specify the application stack size. This option is only applicable for SoCs with external memory. For SoCs with internal memory, the region size is automatically set to 1/8 of the on-chip RAM size. |

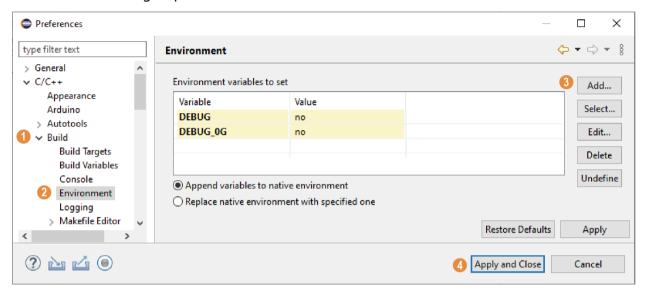

| OpenOCD<br>Debug Mode      | Turn on by default<br>Turn off by default                                                                    | Choose whether you want software applications to run in debug mode by default or not. See <b>Debug with the OpenOCD Debugger</b> on page 42 for more details.                                                                     |

#### **Table 4: Sapphire UART Tab Parameters**

Where n is 0, 1, or 2

| Parameter           | Options | Description                                                                             |

|---------------------|---------|-----------------------------------------------------------------------------------------|

| UART n              | On, off | On: Instantiate the interface. Off: Do not use the interface.                           |

| UART n Interrupt ID | 1 - 36  | Choose the interrupt ID for the UART. The IDs default to: UART 0: 1 UART 1: 2 UART 2: 3 |

### **Table 5: Sapphire SPI Tab Parameters**

Where n is 0, 1, or 2.

| Parameter               | Options | Description                                                                                              |

|-------------------------|---------|----------------------------------------------------------------------------------------------------------|

| SPI n                   | On, off | On: Instantiate the interface. Off: Do not use the interface.                                            |

| SPI n Interrupt ID      | 1 - 36  | Choose the interrupt ID for the SPI. The IDs default to:<br>SPI 0: 4<br>SPI 1: 5<br>SPI 2: 6             |

| SPI n Data Width        | 8 - 16  | Configure the data width for the SPI interface.  Note: Only applicable for SPI 1 and SPI 2.              |

| SPI n Chip Select Width | 1 - 8   | Choose the number of Chip select required for the SPI interface.  Note: Only applicable for SP1 and SP2. |

#### **Table 6: Sapphire I2C Tab Parameters**

Where n is 0, 1, or 2.

| Parameter          | Options | Description                                                           |

|--------------------|---------|-----------------------------------------------------------------------|

| I2C n              | On, off | On: Instantiate the interface.                                        |

|                    |         | Off: Do not use the interface.                                        |

| I2C n Interrupt ID | 1 - 36  | Choose the interrupt ID for the I <sup>2</sup> C. The IDs default to: |

|                    |         | I2C 0: 8                                                              |

|                    |         | I2C 1: 9                                                              |

|                    |         | I2C 2: 10                                                             |

#### **Table 7: Sapphire GPIO Tab Parameters**

Where n is 0 or 1.

| Parameter             | Options        | Description                                                                     |

|-----------------------|----------------|---------------------------------------------------------------------------------|

| GPIO n                | On, off        | On: Instantiate the interface. Off: Do not use the interface.                   |

| GPIO n Bit Width      | 1, 2, 4, 8, 16 | Choose the number of pins for the GPIO. Default: 4 (GPIO 0), 8 (GPIO 1)         |

| GPIO n Interrupt ID 0 | 1 - 36         | Choose the interrupt ID for the GPIO. The IDs default to: GPIO 0: 12 GPIO 1: 14 |

| GPIO n Interrupt ID 1 | 1 - 36         | Choose the interrupt ID for the GPIO. The IDs default to: GPIO 0: 13 GPIO 1: 15 |

#### **Table 8: Sapphire APB3 Tab Parameters**

Where n is 0, 1, 2, 3, or 4.

| Parameter              | Options                                                    | Description                                                                       |

|------------------------|------------------------------------------------------------|-----------------------------------------------------------------------------------|

| APB Slave Address Size | 4KB, 8KB, 16KB,<br>32KB, 64KB, 128KB,<br>256KB, 512KB, 1MB | Choose the APB slave size. This setting applies to all APB slaves.  Default: 64KB |

| APB3 Slave n           | On, off                                                    | On: Instantiate the interface. Off: Do not use the interface.                     |

#### **Table 9: Sapphire AXI4 Tab Parameters**

Where n is 0 or 1.

| Parameter                  | Options                                                                                                                                            | Description                                                                                                                 |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| AXI Slave                  | On, off                                                                                                                                            | On: Instantiate the interface. Off: Do not use the interface.                                                               |

| AXI Slave Size             | 1 KB, 2 KB, 4 KB, 8<br>KB, 16 KB, 32 KB,<br>64 KB, 128 KB, 256<br>KB, 512 KB, 1 MB,<br>2 MB, 4 MB, 8 MB,<br>16 MB, 32 MB, 64 MB,<br>128 MB, 256 MB | Choose the size of the AXI slave.                                                                                           |

| AXI Master n               | On, off                                                                                                                                            | On: Instantiate the interface. Off: Do not use the interface.                                                               |

| AXI Master n Data<br>Width | 32, 64, 128, 256, 512                                                                                                                              | Choose the width of the AXI master.  Do not specify an AXI master width that is larger than the external memory data width. |

#### **Table 10: Sapphire User Interrupt Tab Parameters**

Where n is A, B, C, D, E, F, G, or H.

| Parameter           | Options | Description                                |  |

|---------------------|---------|--------------------------------------------|--|

| User n Interrupt    | On, off | On: Instantiate the interface.             |  |

|                     |         | Off: Do not use the interface.             |  |

| User n Interrupt ID | 1 - 36  | Choose the interrupt ID. The defaults are: |  |

|                     |         | User A Interrupt: 16                       |  |

|                     |         | User B Interrupt: 17                       |  |

|                     |         | User C Interrupt: 22                       |  |

|                     |         | User D Interrupt: 23                       |  |

|                     |         | User E Interrupt: 24                       |  |

|                     |         | User F Interrupt: 25                       |  |

|                     |         | User G Interrupt: 26                       |  |

|                     |         | User H Interrupt: 27                       |  |

#### **Table 11: Sapphire User Timer Tab Parameters**

Where n is 0, 1, or 2.

| Parameter                       | Options    | Description                                                                                   |

|---------------------------------|------------|-----------------------------------------------------------------------------------------------|

| User Timer n                    | On, off    | On: Instantiate the interface. Off: Do not use the interface.                                 |

| User Timer n Counter<br>Width   | 12, 16, 32 | Choose the counter bit width. Default: 12                                                     |

| User Timer n Prescaler<br>Width | 8, 16      | Choose the prescaler bit width. Default: 8                                                    |

| User Timer n Interrupt<br>ID    | 1 - 36     | Choose the interrupt ID. The defaults are: User Timer 0: 19 User Timer 1: 20 User Timer 2: 21 |

**Table 12: Sapphire Base Address Tab Parameters**

| Parameter                         | Options      | Description                                                                                                                                                                                                                                                 |  |

|-----------------------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Address Assignment<br>Method      | AUTO, MANUAL | AUTO: Automatically assign an address to the enabled peripherals.  MANUAL: The user can assign addresses to the enabled peripherals.                                                                                                                        |  |

| External Memory Base<br>Address   | -            | Displays the base address. You cannot change it.                                                                                                                                                                                                            |  |

| AXI Slave Base Address            | _            | Displays the base address when the <b>Address Assignment Method</b> is                                                                                                                                                                                      |  |

| Peripheral and IO Base<br>Address | -            | set to AUTO.  When the <b>Address Assignment Method</b> is <b>Manual</b> , enter the base address value. The wizard automatically rounds the value to 16 MB aligned addresses during IP generation. For example, 0x41234567 is rounded to 0x41000000.       |  |

| UARTn Address Offset              | _            | Displays the base address when the <b>Address Assignment Method</b> set to AUTO.  When the <b>Address Assignment Method</b> is <b>Manual</b> , enter base                                                                                                   |  |

| SPIn Address Offset               | _            |                                                                                                                                                                                                                                                             |  |

| I2Cn Address Offset               | _            | address value. The wizard automatically rounds the value to 4 KB                                                                                                                                                                                            |  |

| GPIOn Address Offset              | _            | aligned addresses during IP generation. For example, 0x41230 is rounded to 0x41000.                                                                                                                                                                         |  |

| User Timern Address Offset        | _            |                                                                                                                                                                                                                                                             |  |

| APB3 Slave n Address Offset       | -            | Displays the base address when the <b>Address Assignment Method</b> is set to AUTO.                                                                                                                                                                         |  |

|                                   |              | When the <b>Address Assignment Method</b> is <b>Manual</b> , enter base address value. The wizard automatically rounds the value to APB sized aligned addresses during IP generation. For example, if the APB size is 64 KB, 0x23456 is rounded to 0x20000. |  |

| On-Chip RAM Base Address          | -            | Displays the base address. You cannot change it.                                                                                                                                                                                                            |  |

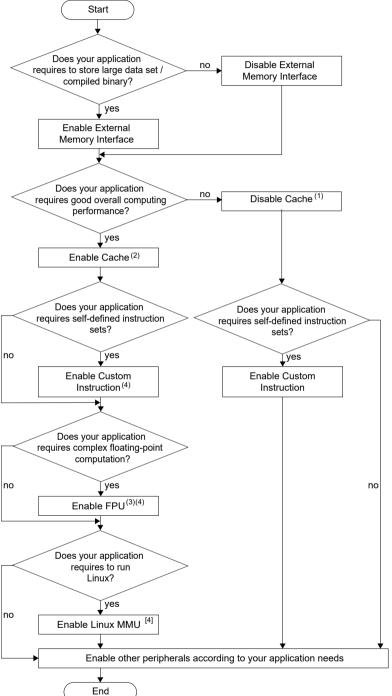

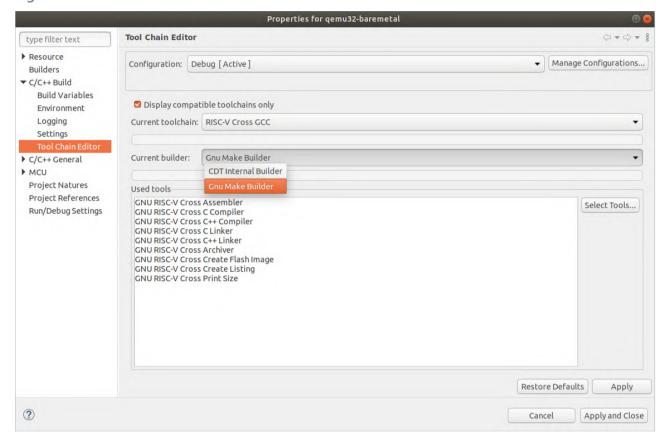

### **SoC Configuration Guideline**

Sapphire SoC is highly adaptive to different use cases. It is configurable to get the best balance between performance and resources. The following flow chart is a simple guideline to help you choose the configuration that suits your needs.

**Figure 3: Sapphire Soc Configuration Guideline**

#### Notes:

- Using the SoC with an external memory interface but without a cache sharply impacts the SoC's overall performance.

- 2. Enabling the cache controller increases the efficiency of processing the instructions but consumes more RAM blocks.

- The SoC calculates faster and more efficiently in floating-point computing if FPU is enabled, but it consumes more FPGA LUTs and RAM blocks.

- 4. When enabling custom instructions, the FPU and the Linux impact the **f**<sub>MAX</sub> performance.

### Modify the Bootloader

When you generate the Sapphire SoC, the IP Manager creates a pre-built bootloader .bin to target the on-chip RAM size you selected. If you assigned the peripheral addresses manually, you need to create a custom bootloader according to the following instructions.

**Learn more:** You need the embedded software example code to make these changes; if you have not already done so, generate it.

**Note:** The pre-build bootloader binaries only use a single data line SPI. To utilize dual or quad data line SPI, refer to **Modify the Bootloader Software to Enable Multi-Data Lines** on page 20.

#### Modify the Bootloader Software to Extend the External Memory Size

First you need to modify the bootloader code:

- Open the bootloaderConfig.h file in the embedded\_sw/<SoC module>/bsp/efinix/ EfxSapphireSoc/app directory.

- 2. Change the #define USER\_SOFTWARE\_SIZE parameter for the new on-chip RAM size and save.

- 3. If you are using the MX25 flash device (e.g., Ti180J484 development kit), incorporate the following step into the bootloader application's makefile. Add CFLAGS+=-DMX25 FLASH before the line LDSCRIPT?=\${BSP PATH}linker/bootloader.Id

**Note:** The addition of **CFLAGS+=-DMX25\_FLASH** ensures that the necessary commands specific to the MX25 flash device are included in your build process.

**4.** In Efinity RISC-V Embedded Software IDE, import **standalone/bootloader** project. Build the project to generate new **bootloader.hex** file.

Second, you update and re-generate the SoC in the IP Manager to point to your new **bootloader.hex** and change the application region size. The default maximum size is 124 KB.

- 1. In the Sapphire IP wizard, go to the Cache/Memory tab.

- 2. Turn on the Custom On-Chip RAM Application option.

- 3. Click the **Browse** button for the to select the new **bootloader.hex** you created in the previous set of steps.

- 4. Generate the SoC.

#### Modify the Bootloader Software without External Memory Enabled

First, you need to modify the bootloader linker script:

- Open the bootloader.ld file in the embedded\_sw/<SoC module>/bsp/efinix/ EfxSapphireSoc/linker directory.

- 2. Replace the MEMORY and PHDRS code with the following code. The <bootloader\_address> should be 0xF9000000 + (<memory size>-1024), where <memory size> is your SoC's on-chip RAM size.

```

MEMORY

{

start (wxai!r) : ORIGIN = 0xF9000000, LENGTH = 512

ram (wxai!r) : ORIGIN = <bootloader_address>, LENGTH = 1024

}

PHDRS

{

start PT_LOAD;

ram PT_LOAD;

}

```

Second you need to modify the bootloader code:

- Open the bootloaderConfig.h file in the embedded\_sw/<SoC module>/bsp/efinix/ EfxSapphireSoc/app directory.

- 2. Change the #define USER\_SOFTWARE\_SIZE parameter for the new on-chip RAM size and save.

- 3. If you are using the MX25 flash device (e.g., Ti180J484 development kit), incorporate the following step into the bootloader application's makefile. Add CFLAGS+=-DMX25 FLASH before the line LDSCRIPT?=\${BSP PATH}linker/bootloader.Id

**Note:** The addition of **CFLAGS+=-DMX25\_FLASH** ensures that the necessary commands specific to the MX25 flash device are included in your build process.

**Note:** If the new compiled bootloader does not fit into the allocated RAM, enable the following optimization in the makefile; DEBUG?=no, BENCH?=yes. Refer to Optimization Settings on page 33.

In Efinity RISC-V Embedded Software IDE, import **standalone/bootloader** project. Build the project to generate new **bootloader.hex** file.

#### Modify the Bootloader Software to Enable Multi-Data Lines

Before you can utilize the multi-data lines SPI in your bootloader, verify whether your board's flash drive supports Dual or Quad I/O modes.

In the Efinity RISC-V Embedded Software IDE example design, data ports 0 and 1 are exclusively connected. If you intend to use the Quad SPI for data transfer, you must establish connections for data ports 2 and 3. The following table shows the number of connected data lines interfacing with the respective FPGAs and flash devices.

Table 13: Multi-Data Lines Interface with FPGAs and Flash Devices

| Development Kit      | Flash Device     | Number of Data Lines Connected |

|----------------------|------------------|--------------------------------|

| T8BGA81              | W25Q80DLSNIG     | 2                              |

| T20BGA256            | W25Q32JVSSIQ     | 2                              |

| T120BGA324           | W25Q128JVSIQ     | 4                              |

| T120BGA576           | W25Q128JVSIQ     | 4                              |

| Xyloni               | W25Q128JVSIM     | 2                              |

| Ti60F225             | W25Q64JWSSIQ     | 2                              |

| Ti180J484/ Ti180M484 | MX25U25645GZ4I00 | 4                              |

In the **bootloaderConfig.h** file, you can define the configurations by selecting from the various data line modes:

SINGLE SPI: Single data line

DUAL SPI: Dual data line

QUAD SPI: Quad data line

Note: If the flash device is MX25 (from Ti180J484 development kit), add CFLAGS+=-DMX25\_FLASH before the LDSCRIPT?=\${BSP\_PATH}linker/bootloader.Id into the bootloader application's makefile. Defining the MX25 includes the required commands specific to the MX25 flash device.

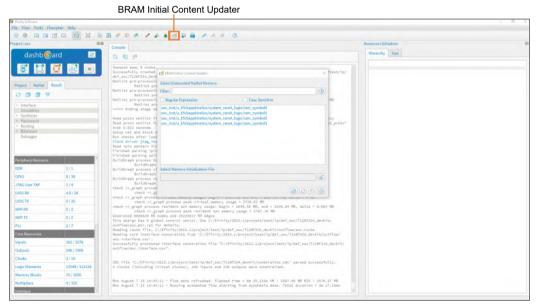

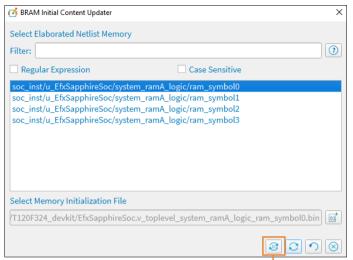

#### Updating Bootloader with Efinity BRAM Initial Content Updater

The Efinity BRAM Initial Content Updater provides a convenient way to modify the default firmware (either bootloader or other application) within the Sapphire SoC onchip RAM. This process enables you to update the on-chip RAM initial content without recompiling the entire project.

To update the on-chip RAM initial content, follow these steps:

- 1. Compile and locate the .hex file: Compile your new application in Efinity RISC-V Embedded Software IDE and locate the corresponding .hex file that contains the compiled code.

- 2. Generate the Sapphire SoC with the new application: By using the Sapphire SoC IP Configurator, update the default on-chip RAM application with your new application compiled in the provious step. You may refer to the Modify the Bootloader Software to Extend the External Memory Size on page 19 on how to use the Custom On-Chip RAM Application in the Sapphire SoC IP Configurator. and you are now ready for the updating process.

- 1

**Note:** You may opt to generate the binaries with the **binGen.py** helper script provided manually. Refer to **Appendix: Re-Generate the Memory Initialization Files Manually** on page 177.

- 3. Locate the new binaries for your application: After the Sapphire SoC is generated with your application, locate the new binaries, **EfxSapphireSoc.v\_toplevel\_system\_ramA\_logic\_ram\_symbol<n>.bin** where <n> is the range from 0 to 3 (up to 7 if FPU extension is enabled).

- **4.** Open the BRAM Initial Content Updater: Click at the **BRAM Initial Content Updater** tab to launch the **BRAM Initial Content Updater**.

Figure 4: Open the BRAM Initial Content Updater

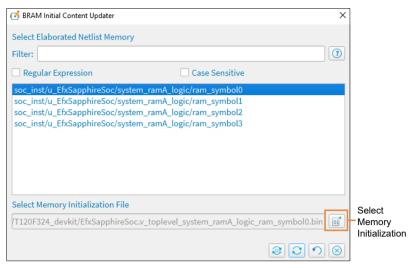

5. Select Memory Initialization File: In the **BRAM Initial Content Updater** window, locate the Sapphire SoC BRAM that you would like to update and click on the \*\_symbol0. In the **Select Memory Initialization File** section, click the **Select Memory Initialization** tab. Browse to the updated

EfxSapphireSoc.v toplevel system ramA logic ram symbol<n>.bin and click Open.

**Figure 5: Select Memory Initialization File**

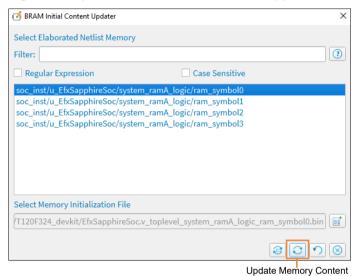

**6.** Update the BRAM: Click on the **Update Memory Content** tab to update the **symbol0** BRAM with the new application **symbol0** binary.

Figure 6: Update the BRAM with New Application

- 7. Update the remaining BRAM: Repeat step 5 and 6 for all the available symbol files. Update the BRAM with the corresponding binary. For example, update \* ram symbol2 BRAM with

- EfxSapphireSoc.v toplevel system ramA logic ram symbol2.bin binary file.

**8.** Generate the new bitstream: Click on the **Regenerate Bitstream** icon to regenerate the bitstream. The generated new bitstreams are located in the outflow folder.

**Figure 7: Generate the New Bitstream**

#### Note:

For more information on the Efinity BRAM Initial Content Updater and its application, see Efinity Software User Guide.

# Program the Board with the Sapphire RTL Design

#### **Contents:**

- About the Example Design

- Enable the On-Board 10 MHz Oscillator (T120 BGA324 Board)

- Enable the LPDDR4x Memory (Ti180 J484 Board)

- Installing USB Drivers

- Program the Development Board

Before working with software code, 易灵思 recommends that you program your board with an RTL design that instantiates the Sapphire SoC. When you generate the Sapphire SoC with the IP Manager, you can optionally generate an example Efinity® project and bitstream file to get you started quickly.

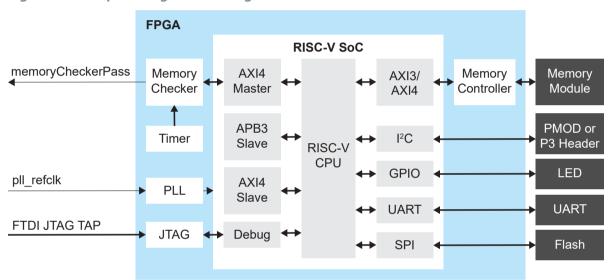

### About the Example Design

This example targets Trion and 钛金系列 development boards:

- Trion® T120 BGA324 Development Board—The RTL design files are in the T120F324 devkit directory.

- 钛金系列 Ti60 F225 Development Board—The RTL design files are in the **Ti60F225\_devkit** directory.

- 钛金系列 Ti180 J484 Development Board—The RTL design files are in the **Ti180J484\_devkit** directory.

When you generate the IP core, the IP Manager creates the example design (PLL settings, SDC timing constraints, and I/O assignments) using the settings you chose in the wizard, with a few exceptions:

- For the Trion board, the example design only supports external memory widths of 128 and 256 bits because the DDR controller only supports these widths. Therefore, do not choose 32 or 64 bits for the external memory.

- The example design automatically connects UARTO, SPIO, I2CO, GPIOO, the soft TAP pins, and the PLL source clock pins to top-level ports, and it assigns I/O pins to them (if they are enabled). If you add more of these peripherals, you need to connect them manually and create the I/O assignments for them.

- The example design uses PLL settings that look for the best effort multiplier and divider values.

Note: The following description is for the example design using the default settings.

This example writes to and reads from the development board's memory module using the AXI interface:

- For the Trion® T120 BGA324 Development Board, the design uses the board's LPDDR3 DRAM module.

- For the 钛金系列 Ti60 F225 Development Board, the design uses the board's HyperRAM module.

- For the 钛金系列 Ti180 J484 Development Board, the design uses the board's LPDDR4/LPDDR4x DRAM module.

#### The Sapphire SoC is configured for:

- 100 MHz frequency

- External memory interface is enabled with a width of 128 and size of 3.5 GB

- Caches are enabled with both Data Cache and Instruction Cache set to one way with cachesize of 4 KB

- 4KB on-chip RAM size

- Soft Debug Tap is disabled

- UART 0 is enabled

- SPI 0 is enabled

- I2C 0 is enabled

- GPIO 0 is enabled

- APB3 0 is enabled

- AXI4 Slave is enabled

- AXI Master 0 is enabled

- User interrupt A is enabled

Figure 8: Example Design Block Diagram

**Table 14: Example Design Implementation**

| FPGA              | Logic +<br>Adders | Flipflops | Multipliers<br>or DSP<br>Blocks | Memory<br>Blocks | f <sub>MAX</sub> (MHz) | Language    | Efinity<br>Version |

|-------------------|-------------------|-----------|---------------------------------|------------------|------------------------|-------------|--------------------|

| T120<br>BGA324 C4 | 8,830             | 8,919     | 4                               | 70               | 107                    | Verilog HDL | 2023.1             |

| Ti60 F225 C4      | 11,178            | 9,973     | 4                               | 82               | 180                    | Verilog HDL | 2023.1             |

| Ti180 J484 C4     | 12,213            | 15,866    | 4                               | 100              | 146                    | Verilog HDL | 2023.1             |

Note: All example designs are constrained with a 100 MHz system clock.

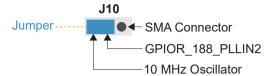

## Enable the On-Board 10 MHz Oscillator (T120 BGA324 Board)

For the Trion® T120 BGA324 Development Board, the SoC design uses the on-board 10 MHz oscillator. To enable it, add a jumper to connect pins 2 and 3 on header J10.

Figure 9: Connect Pins 2 and 3 on J10

### Enable the LPDDR4x Memory (Ti180 J484 Board)

For the 钛金系列 Ti180 J484 Development Board, the SoC design uses LPDDR4x settings to drive the external memory. To enable it, change the jumpers on PT12 and PT15 to connect pins 1 and 2 to provide 0.6 V to VDDQ and VDDQ\_PHY.

Figure 10: Connect Pins 1 and 2 on PT12 and PT15

### **Installing USB Drivers**

To program Trion® FPGAs using the Efinity® software and programming cables, you need to install drivers.

易灵思 development boards have FTDI chips (FT232H, FT2232H, or FT4232H) to communicate with the USB port and other interfaces such as SPI, JTAG, or UART. Refer to the 易灵思 development kit user guide for details on installing drivers for the development board.

**Note:** If you are using more than one 易灵思 development board, you must manage drivers accordingly. Refer to AN 050: Managing Windows Drivers for more information.

#### **Installing Drivers on Windows**

On Windows, you use software from Zadig to install drivers. Download the Zadig software (version 2.7 or later) from **zadig.akeo.ie**. (You do not need to install it; simply run the downloaded executable.)

Install the driver for the interfaces listed in the following table.

| Board                                | Interface to Install Driver                                                                                                                              |  |

|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Trion® T120 BGA324 Development Board | Install drivers for all interfaces (0 and 1).                                                                                                            |  |

| 钛金系列 Ti60 F225 Development Board     | Install drivers for interfaces 0 and 1 only. Windows automatically installs a driver for interfaces 2 and 3 when you connect the board to your computer. |  |

| 钛金系列 Ti180 J484 Development Board    | Install driver for interface 1 only.                                                                                                                     |  |

#### To install the driver:

- 1. Connect the board to your computer with the appropriate cable and power it up.

- 2. Run the Zadig software.

**Note:** To ensure that the USB driver is persistent across user sessions, run the Zadig software as administrator.

- 3. Choose Options > List All Devices.

- **4.** Repeat the following steps for each interface. The interface names end with (Interface N), where N is the channel number.

- Select libusb-win32 in the Driver drop-down list.

- Click Replace Driver.

- 5. Close the Zadig software.

**Note:** This section describes the instruction to install the libusb-win32 driver for each interface separately. If you have previously installed a composite driver or installed using libusbK drivers, you do not need to update or reinstall the driver. They should continue to work correctly.

#### **Installing Drivers on Linux**

The following instructions explain how to install a USB driver for Linux operating systems.

- 1. Disconnect your board from your computer.

- 2. In a terminal, use these commands:

```

> sudo <installation directory>/bin/install_usb_driver.sh

> sudo udevadm control --reload-rules

```

**Note:** If your board was connected to your computer before you executed these commands, you need to disconnect and re-connect it.

### Program the Development Board

When you generate the Sapphire SoC in the IP Manager, you can optionally generate an example design targeting an 易灵思 development board. Example designs include a bitstream file, **soc.hex**, so you can get started quickly without having to compile the design.

**Table 15: Available Example Designs**

| Board                                | Location         |

|--------------------------------------|------------------|

| 钛金系列 Ti60 F225 Development Board     | Ti60F225_devkit  |

| 钛金系列 Ti180 J484 Development Board    | Ti180J484_devkit |

| Trion® T120 BGA324 Development Board | T120F324_devkit  |

Download the .hex file to the board using these steps:

Connect the board to your computer using a USB cable.

#### Learn more:

Instructions on how to use the Efinity software and board documentation are available in the Support Center. .

### **Simulate**

The IP Manager automatically generates a testbench and top-level file for simulation based on the settings you made in the wizard, including the top-level file generation, I/O connection to the testbench, simulation models, and stimulus such as clock and reset. The testbench bypasses the SPI flash data retrieval step to speed up simulation.

Note: If you manually assign addresses to the peripherals, the default simulation may not function correctly.

- 1. Open a terminal.

- 2. Change to the **Testbench** directory for your SoC.

- **3.** Set up the Efinity environment:

- Linux: source /<path to Efinity>/bin/setup.sh

- Windows: c:\<path to Efinity>\bin\setup.bat

- **4.** Run the simulation using the default application with the command Python3 run.py.

Note: If you want to include the SPI flash retrieval step, run the simulation with the command:

```

Python3 run.py -f

```

A successful simulation returns the following messages

To simulate with a different application instead of the default, use the command:

```

Python3 run.py -b <path to application>/app.bin

```

When you use a non-default application, the testbench bypasses the default driver and monitor sequences and displays warning messages.

You need to develop your own sequence for your application.

### Launch Efinity RISC-V Embedded Software IDE

#### **Contents:**

- Sapphire SoC IDE Backward Compatibility

- Launching the Efinity RISC-V Embedded Software IDE

- Optimization Settings

### Sapphire SoC IDE Backward Compatibility

The Efinity software v2022.2 and higher includes the Efinity RISC-V Embedded software IDE for developing RISC-V software applications. Previously, you developed software using the open-source RISC-V SDK. The IDE provides an enhanced environment for developing embedded applications, and 易灵思 recommends that all users switch to it. The IDE has these features and advantages:

- Optimized process for importing projects

- Eliminates redundant steps to import C/C++ Project Settings

- Simplifies the sample projects import process with tick boxes