# Hardware changes on ADC and DAC for JESD204B Tx and RX Porting on Elitestek FPGA

Date: 25<sup>th</sup> February 2025

## Contents

| 1 | DAC Hardware changes2 |

|---|-----------------------|

| 2 | ADC Hardware changes  |

# **1** DAC Hardware changes

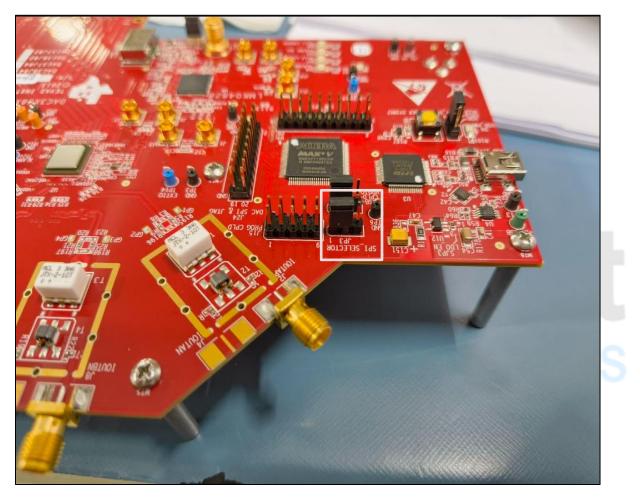

1. For SPI header position changed to 1-2 for configuration through FPGA

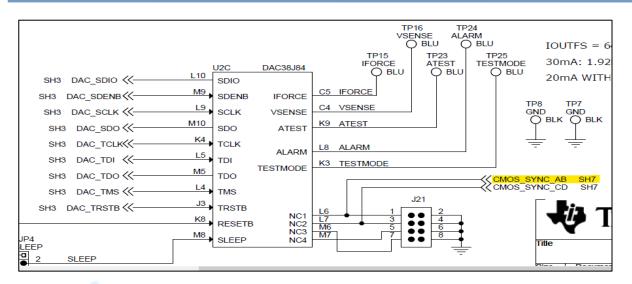

2. SYNC from header J21 mapped to FMC\_SYSREF, which is mapped on the FMC connector

3. The following changes are made to test deterministic latency

To prove the deterministic latency, the sample trigger needs to be mapped to the GPIO header, but the Elitestek Evaluation board doesn't have any GPIO's, also the DAC card doesn't have any GPIO's mapped to any of the header. So, the following changes are made to map the trigger signal:

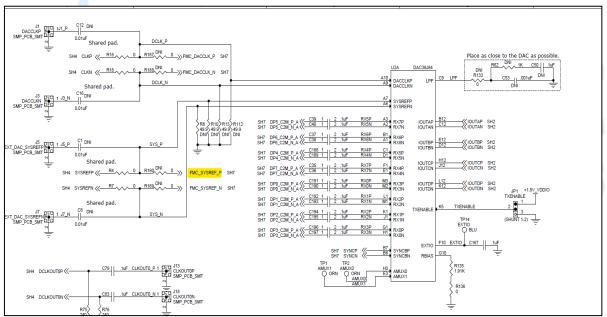

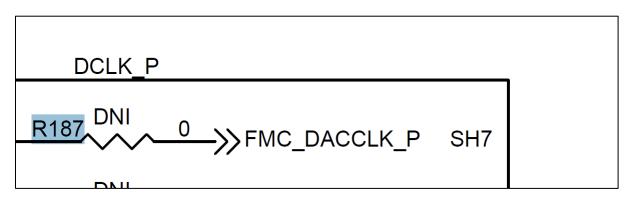

- > The FMC\_DACCLK\_P signal from the FPGA is not used in the current design.

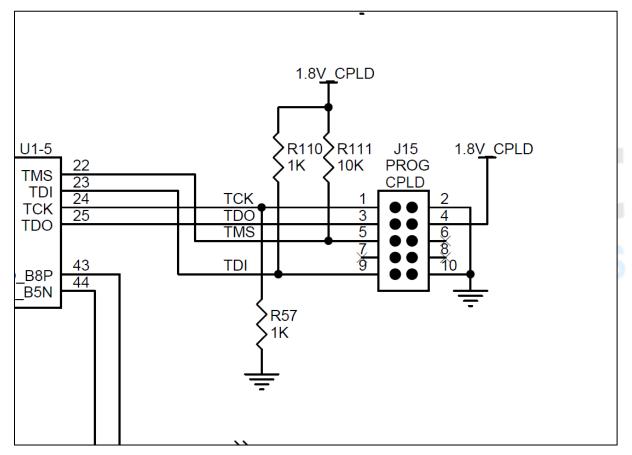

- The signal R187 on the DAC EVM has a DNP resistor. Connect a wire from one pad of the resistor on the FMC side to the J15 header PIN 7.

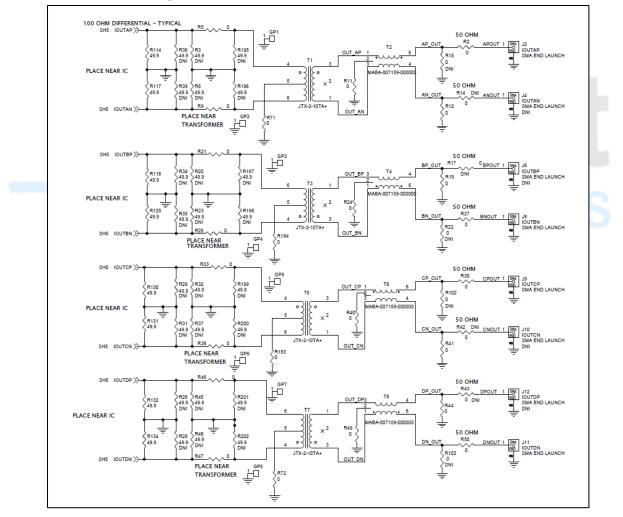

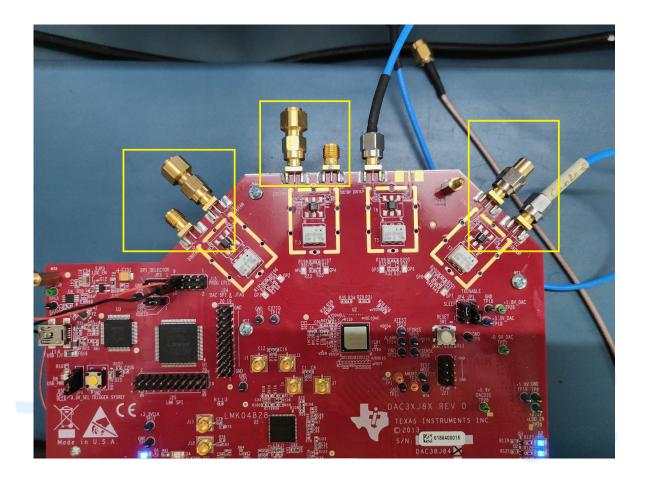

4. The following changes are made to get the same output on all DAC outputs.

There were SMA connectors mapped on alternate polarities on channel AB and CD. To get same output on all the channels **add the SMA female connectors on other polarities wherever they are not present.**

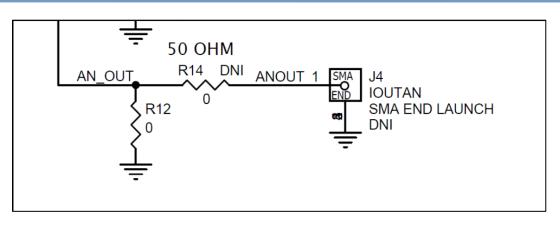

- > The R14 is mounted with 0 ohm and R12 0 ohm resistor is removed from the board.

- > The J4 is mounted with SMA female header (similar changes are done for other paths).

- To make sure there is no impedance mismatch in the transmission lines, 50-ohm termination was used on SMA connectors.

> Similar changes need to be made for other channels, where the P side is not mounted

- 5. External VCXO input :

- Due to the less PDF2 value for PLL2, there was jitter on output clock which is the cause of 1.6ns variation in the output.

- So to reduce this jitter on the output clock we need to change the VCXO clock input to the LMK chip, since there is only 122.88 MHz VCXO on board, we cannot change that.

- > Hence, we need to give a clock directly from some external source.

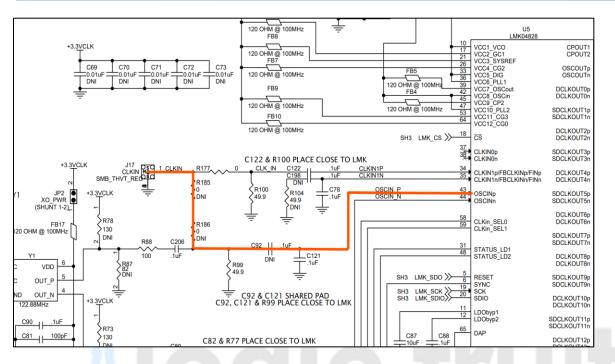

- On board there is no SMA on the OSCIN pin on LMK, so we will be using CLKIN1 SMA for this external input and through some register changes we will enable the path from CLKIN1 to OSCIN input of LMK.

#### To enable the highlighted path, we need to do following modifications

| Reference | current state | Requirement | Remarks      |

|-----------|---------------|-------------|--------------|

| R177      | 0 ohm         | DNP         | Required     |

| R185      | DNP           | 0 ohm       | Required     |

| R186      | DNP           | 0 ohm       | Required     |

| C92       | DNP           | 0.1uF       | Required     |

| C121      | 0.1uF         | DNP         | Required     |

| R77       | 49.9 ohm      | 0 ohm       | Not Required |

| C80       | 0.1uF         | DNP         | Required     |

| C206      | 0.1uF         | DNP         | Required     |

### 2 ADC Hardware changes

- While testing the 40X PLL mode, the PLL was locked, but the output of the clock buffer used on the LMK to ADC path was noisy and the clock frequency was unexpected (some randomly changing frequency was observed on the scope).

- 2. The clock buffer datasheet recommends adding a 100ohm termination at the input for LVDS clock input because the clock buffer input is high impedance. But on the eval board there was no termination on the input.

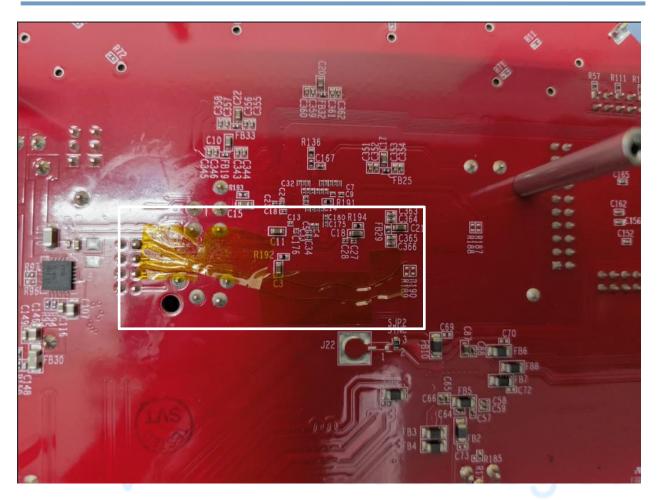

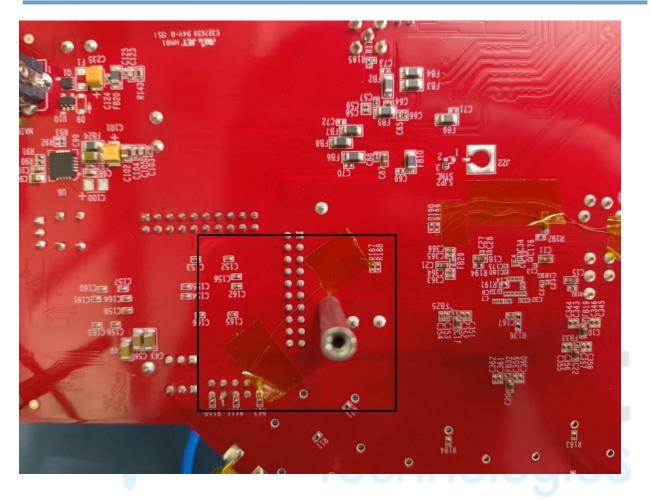

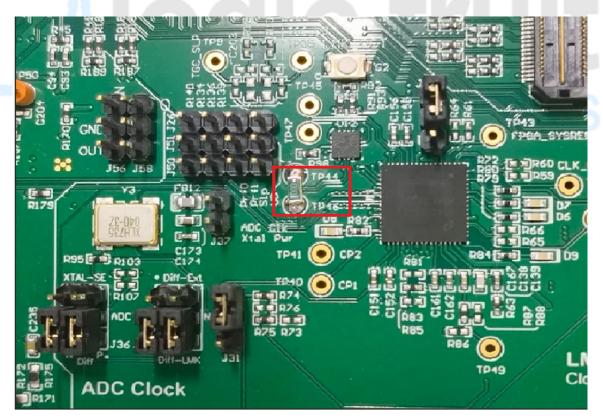

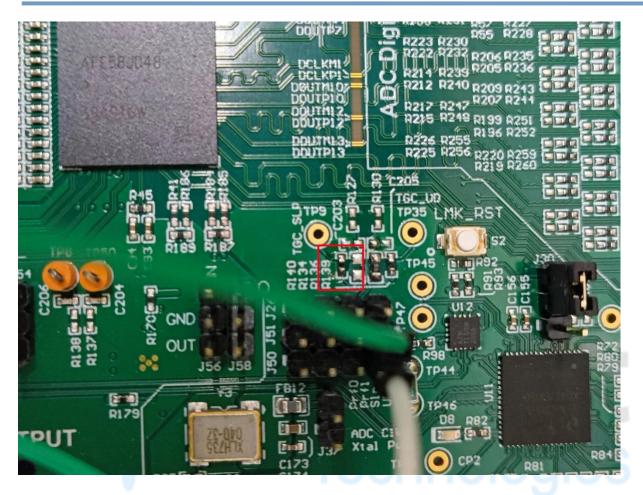

- 3. To overcome this issue, we added a 100ohm termination between the test points (TP44 and TP46) provided on board on the differential clock output

|                                                   | TP40                     |                                            |

|---------------------------------------------------|--------------------------|--------------------------------------------|

| CPOUT<br>CPOUT2                                   | 32 CPI DNP TP41          |                                            |

| F CSCOUT<br>OSCOUT                                |                          |                                            |

| JT DCLKOUTO<br>DCLKOUTO                           | 2 FPGA GTXCLK M<br>TP43. | FPGA_GTXCLK_P > FPGA_GTXCLK_M >            |

| SDCLKOUT1<br>SDCLKOUT1                            | 4 FPGA SYSREFM           | FPGA_SYSREFP<br>FPGA_SYSREFM               |

| DCLKOUT2<br>DCLKOUT2                              |                          | LMK_ADC_CLKP<br>LMK_ADC_CLKN               |

| SDCLKOUT3<br>SDCLKOUT3                            | 14 SYSREFM SERDES        | SYSREFP_SERDES ><br>SYSREFM_SERDES >       |

| 3CLKIN DCLKOUT4<br>FBCLKIN* DCLKOUT4<br>SDCLKOUT5 | 20                       | CW16X_CLEAN_P<br>CW16X_CLEAN_N             |

| SDCLKOUT5<br>DCLKOUT5                             |                          | CW1X_CLEAN_P<br>CW1X_CLEAN_N<br>CPLD_CLK_P |

| DCLKOUT6<br>SDCLKOUT7                             | 28                       | CPLD_CLK_M >                               |

| SDCLKOUT7<br>DCLKOUT8                             | DNP                      | FPGA_CLK_OUT_P >                           |

| DCLKOUT8<br>SDCLKOUT5<br>SDCLKOUT9                | 10                       | FPGA_CLK_OUT_M >                           |

| DCLKOUT10                                         |                          |                                            |

The below image is the 100ohm termination done on ADC Evaluation Board

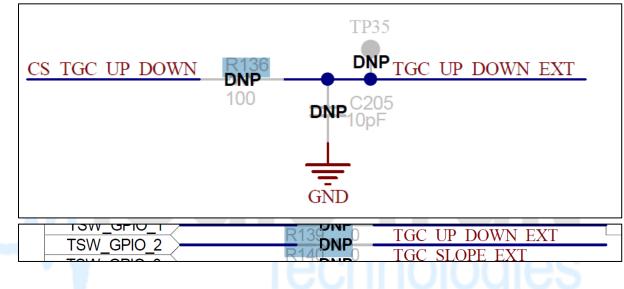

- 6. The following changes are made to prove deterministic latency

- To prove deterministic latency, a square wave needs to be sent from FPGA to the scope and ADC input, for which there is a need for a GPIO header

- Since ELITESTEK EVM has no GPIO connected to the header, the ADC eval board spare header will be used.

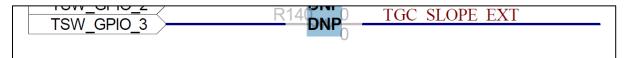

- The TSW\_GPIO\_2 will be used for this purpose, but there are two DNP resistors between the path, which need to mound.

- The resistor references are R139 and R136, and zero-ohm resistors are mounted on them.

- Another GPIO is needed to prove deterministic latency, here an ADC\_MSB signal from FPGA must be checked in the scope. For this purpose, one test point or header is required

- Connect the TSW\_GPIO\_3 for this purpose, but there is one DNP resistor in between the path, which needs to be mounted. The resistor references are R140, so mount zero-ohm resistors on this.

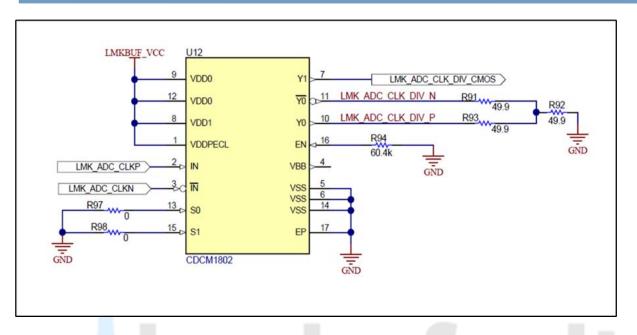

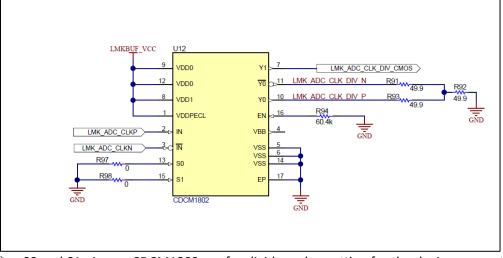

Changed the divider value of buffer in the path of LMK to ADC sampling clock  $\geq$

- S0 and S1 pins on CDCM1802 are for divider value setting for the device, currently it  $\geq$ is set on four that means the buffer will generate a output clock which is /4 of the input clock.

- We need to change this divider to one.

- As per TI this divider in the path can lead to length mismatching and since there is a factor of four between input and output so this can lead to phase variation between SYSREF and Device clock output from this divider. So, it's better to keep this divider to one to remove this ambiguity.

- As per the datasheet to make this divider one we need to change the R97 resistor  $\geq$ value from 0ohm to 60k ohm.

| MODE |                    |                    | 60                 | LVPECL <sup>(1)</sup> | LVCMOS       |

|------|--------------------|--------------------|--------------------|-----------------------|--------------|

| MODE | EN                 | S1                 | S0                 | Y0                    | ¥1           |

| 0    | 0                  | X                  | x                  | Off (high-z)          | Off (high-z) |

| 1    | V <sub>DD</sub> /2 | 0                  | V <sub>DD</sub> /2 | /1                    | /1           |

| 2    | V <sub>DD</sub> /2 | V <sub>DD</sub> /2 | 1                  | /1                    | /2           |

| 3    | 1                  | 0                  | 0                  | /1                    | /4           |

| 4    | V <sub>DD</sub> /2 | 0                  | 1                  | /2                    | /2           |

| 5    | 1                  | 0                  | 1                  | /2                    | /4           |

| 6    | V <sub>DD</sub> /2 | 0                  | 0                  | /4                    | /4           |

| 7    | V <sub>DD</sub> /2 | 1                  | 0                  | /4                    | /8           |

| 8    | V <sub>DD</sub> /2 | V <sub>DD</sub> /2 | V <sub>DD</sub> /2 | /8                    | /1           |

| 9    | 1                  | 1                  | 0                  | /8                    | /4           |

| 10   | 1                  | 1                  | 1                  | Off (high-z)          | /4           |

- (1) The LVPECL outputs are open emitter stages. Thus, if you leave the unused LVPECL output Y0

- unconnected, then the current consumption is minimized and noise impact to remaining outputs is neglectable. Also, each output can be individually disabled by connecting the corresponding VDD input to GND.

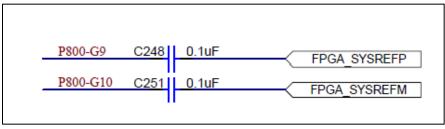

- > Removal of AC caps on the sysref path to FPGA.

- Remove the 0.1uf capacitor on the path and replace it with 0 ohm resistor to improve the slew rate on the sysref path.

- $\circ$   $\,$  Change C248 and C251 on the path to 0ohm resistor.

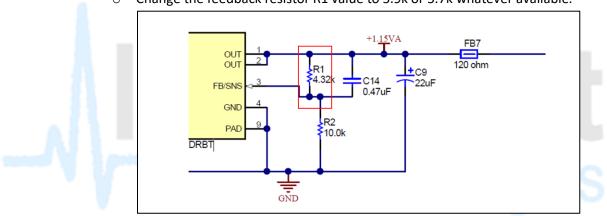

Increase of DVDD\_1V15 swing to improve the amplitude on the FPGA RX side.

$\circ$   $\,$  Change the feedback resistor R1 value to 5.9k or 5.7k whatever available.