# TJ-Series PCIe<sup>®</sup> Controller User Guide

UG-TiPCle-v1.6 June 2025 www.elitestek.com

# **Contents**

| Introduction                                        | 4   |

|-----------------------------------------------------|-----|

| Features                                            | 5   |

| Functional Description                              | 6   |

| Physical Layer                                      |     |

| SRIS Operation                                      |     |

| RX Lane Margining                                   |     |

| Data Link Layer                                     |     |

| Data Link Feature Exchange                          |     |

| Aggregating ACK DLLPs                               |     |

| Transaction Layer                                   |     |

| AXI Application Layer                               |     |

| AXI Master Read Operation                           |     |

| AXI Master Write Operation                          |     |

| End-to-End Data Protection                          |     |

| Inbound Message Interface                           |     |

| Ordering Between AXI Master Write and Read Channels |     |

| Inbound PCIe to AXI Address Translation (Root Port) |     |

| Inbound PCIe to AXI Address Translation (Endpoint)  |     |

| AXI Slave Interface                                 |     |

| AXI Master and Slave Read/Write Length Limitations  |     |

| Interrupt Interface                                 |     |

| Legacy Interrupt Operation                          |     |

| MSI and MSI-X Interrupt Modes                       |     |

| Interrupt Sideband Signals                          |     |

| Clock Sources  Link Control                         | 62  |

| Link Up                                             |     |

| Link Down and Reset                                 | 62  |

| Reset Types                                         | 63  |

| Cold Reset                                          |     |

| Warm Reset                                          |     |

| Hot Reset                                           |     |

| Reset Handshake                                     |     |

| Function-Level Reset (FLR)                          |     |

| Concurrent FLR Request in Multiple PFs/VFs          |     |

| Reset During an FLR                                 | 66  |

| Power Management                                    | 66  |

| Function Power States                               |     |

| L0s Power State                                     |     |

| L1 Power State                                      |     |

| Entering L1 via ASPM                                |     |

| Entering L1 via PCI-PM                              |     |

| L1 Exit Triggers                                    |     |

| L1 Register Programming                             |     |

| Blocking L1 Explicit Client Exit or Endpoint Entry  |     |

| L1 Power Substates                                  |     |

| Entering L1 Substate                                |     |

| Exiting L1 Substate                                 |     |

| L1.1 Operation                                      |     |

| L1.2 Operation                                      |     |

| L1 Substate Register Programming                    |     |

| Explicit Client Exit or Entry Block                 |     |

| Explicit Chart Life of Life y Diook                 | 1 0 |

| Integration Details                                                           |     |

|-------------------------------------------------------------------------------|-----|

| L2 Power State                                                                |     |

| Entering L2                                                                   |     |

| Wake Up or Exiting L2                                                         | 78  |

| Configuring Registers with the APB Interface                                  | 79  |

| Configuration Snoop Interface                                                 | 80  |

| Vendor-Specific Extended Capability (VSEC)                                    | 82  |

| Configuration Guide                                                           | 84  |

| AXI Outbound Access Example                                                   | 84  |

| Accessing the Configuration TLP                                               |     |

| Method 1                                                                      |     |

| Method 2                                                                      |     |

| Programming the Outbound PCIe Descriptor Register                             |     |

| Address Translation                                                           |     |

| Memory or I/O TLP Access  Message TLP Access                                  |     |

| Endpoint Autonomous Link Bandwidth Management                                 |     |

| Programming the SR-IOV Registers                                              |     |

| VF Function Number Allocation                                                 |     |

| Setting up the VF BAR Registers                                               |     |

|                                                                               |     |

| Managing Outbound NP Outstanding Requests and Completion Responses (Endpoint) | 89  |

| Interface Signals                                                             | 92  |

| Clock Signals                                                                 |     |

| Reset Interface Signals                                                       |     |

| AXI Master Interface Signals                                                  |     |

| AXI Slave Interface Signals                                                   |     |

| Interrupt Interface Signals                                                   |     |

| Message Interface SignalsStatus and Error Indicator Signals                   |     |

| Function-Level Reset Signals                                                  |     |

| Configuration Snoop Interface Signals                                         |     |

| Vendor Specific (VSEC) Interface Signals                                      |     |

| Power Management Interface Signals                                            |     |

| L1 Interface Signals                                                          |     |

| L1 Substate Interface Signals                                                 |     |

| APB Interface Signals                                                         | 110 |

| Appendix A: Acronyms and Abbreviations                                        | 111 |

| Appendix B: Error Handling                                                    | 112 |

| Non-Fatal Errors                                                              |     |

| Multiple Errors                                                               | 115 |

| Multiple-Error Scenarios                                                      | 116 |

| Appendix C: LTSSM State Encoding                                              | 117 |

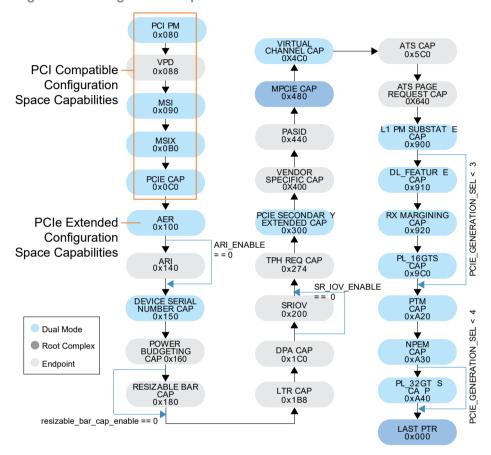

| Appendix D: PCle Configuration Capabilities Linked List                       |     |

| Configuration-Specific Capabilities                                           | 119 |

| Appendix E: Supported Chipsets                                                | 122 |

| Revision History                                                              | 122 |

# Introduction

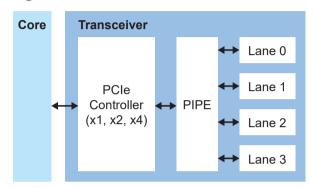

TJ-Series transceivers consist of a physical medium attachment (PMA) and a physical coding sublayer (PCS). The PMA connects the FPGA to the lane, generates the required clocks, and converts the data from parallel to serial or serial to parallel. The PCS contains the digital processing interface between the PMA and the FPGA fabric. The PCS supports SGMII, 10GBase-KR, and PCIe® Gen4 as well as PMA Direct. This user guide provides the specifications for the PCIe Controller interface.

Figure 1: Transceiver Used for PCle

The following table shows the high-level controller configuration. It supports up to Gen4 x4, which is equivalent to a 16 Gbps lane rate or up to 64 Gbps link bandwidth.

**Table 1: PCle Controller Configuration**

| Parameter                                                       | Setting                              |  |

|-----------------------------------------------------------------|--------------------------------------|--|

| Operational mode                                                | Endpoint or root port <sup>(1)</sup> |  |

| Link width                                                      | x1, x2, x4                           |  |

| PIPE interface f <sub>MAX</sub>                                 | 500 MHz, Gen 4                       |  |

|                                                                 | 250 MHz, Gen 3                       |  |

|                                                                 | 125 MHz, Gen 2                       |  |

|                                                                 | 62.5 MHz, Gen 1                      |  |

| PCIe Controller core clock <sup>(2)</sup>                       | 500 MHz                              |  |

| FPGA user clock (AXI interface) f <sub>MAX</sub> <sup>(3)</sup> | 125 - 250 MHz                        |  |

| FPGA user data path width (AXI interface)                       | 256 bits                             |  |

| AXI interface address width                                     | 64 bits                              |  |

| Power management clock f <sub>MAX</sub>                         | 40 MHz                               |  |

The PCIe Controller can be configured to be either endpoint (EP) or root port (RP) mode, depending on your requirements. PCIe operations initiated by the user side are driven through

Root port capabilities are limited in the Efinity® software v2024.1.

<sup>(2)</sup> The PCIe Controller core clock is an internal clock.

This clock, AXI\_CLK, is available to the user application

the AXI4 slave port; PCIe operations initiated by the host side are driven through the AXI4 master port.

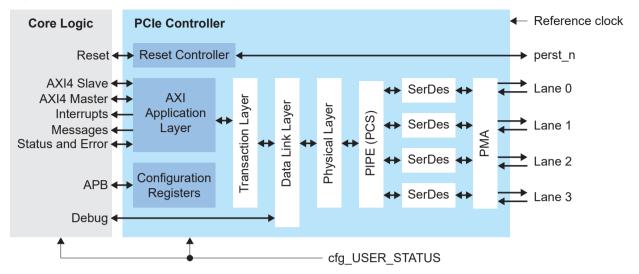

Figure 2: PCle Controller Block Diagram

**Note:** Refer to **Appendix A: Acronyms and Abbreviations** on page 111 for terms used in this document. Refer to "PCI Express Interface" in the **TJ-Series Interfaces User Guide** for configuration options.

# **Features**

- Fully integrated PMA with PIPE interface and controller (consisting of the physical layer, data link layer, and transaction layer)

- Programmable as endpoint (EP) or root port (RP)

- AXI4 slave interface port

- AXI4 master interface port

- Dedicated interrupt interface and inbound message interface supporting conventional interrupts, MSI, and MSI-X

- · Supports:

- Power management

- Function-level reset (FLR)

- \_ SR-IOV

- Up to four physical functions; each physical function can support up to 16 virtual functions

- Up to 64 virtual functions

- Advanced error reporting (AER)

- TLP processing hints (TPH)

- Steering tag

# **Functional Description**

The following figure shows a high-level overview of the PCle Controller. This topic provides an overview of the layers, which are described in detail later.

**AXI4 Slave AXI4 Master** Read/Write Read/Write Interrupt Interface Interface Interface **AXI Application Layer** \$ Configuration Transaction Layer Registers Completion PNP Receive Flow Receive FIFO RAM Control FIFO RAM \$ Data Link Layer Replay Link CRC CRC Buffer Generator State Check RAM Physical Layer LTSSM PIPE Interface

Figure 3: PCle Controller High-Level Block Diagram

### Physical Layer

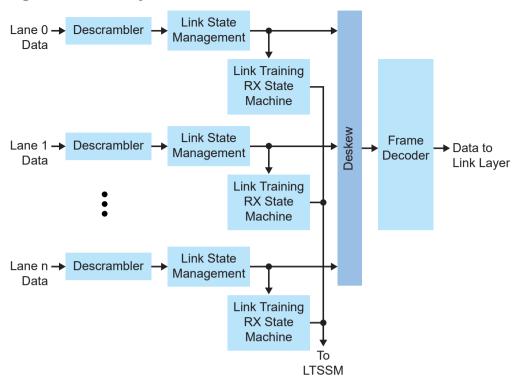

On the physical layer's receive (RX) side, data arrives from the link over the PIPE interface. For all link speeds, each lane is de-scrambled independently. The data from the lanes is de-skewed to generate aligned data. The PCIe Controller decodes the aligned data and sends the packets to the data link layer.

On the physical layer's transmit (TX) side, data arrives from the data link layer over a single interface. The PCIe Controller formats the data into packets by appending SOP and EOP, and aligns it on the outgoing lanes. For all link speeds, the data from each lane is scrambled independently before being transmitted on the outgoing PIPE. The physical layer has one instance of the Link Training and Status State Machine.

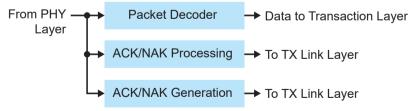

### Data Link Layer

The data link layer receives packet data from the physical layer's RX. A CRC checker checks the incoming packet LCRC. The PCIe Controller sends the LCRC-stripped data to the transaction layer. A separate state machine performs the data link layer initialization.

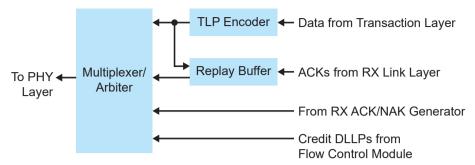

On the TX side, the data link layer receives packets from the transaction layer over a 128-bit data path. It then adds the LCRC to the packets, multiplexes them with other data link layer packets (such as ACKs and flow control DLLPs), and forwards them to the physical layer. The TX side of the data link layer also has the replay buffer that is required for re-transmitting packets.

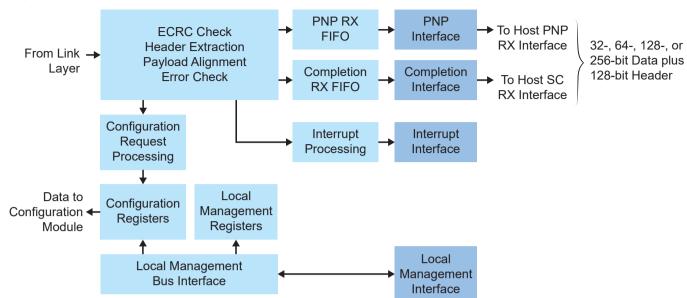

### **Transaction Layer**

At the transaction layer, data arrives on the RX side from the data link layer. The arriving packets go into a receive FIFO buffer, and packet forwarding only begins when the FIFO buffer has a complete packet. Packets are decoded and forwarded to the appropriate host interface, or to an internal module (for example, interrupt messages). The host interfaces include separate interfaces for posted/non-posted (PNP) and completion packets.

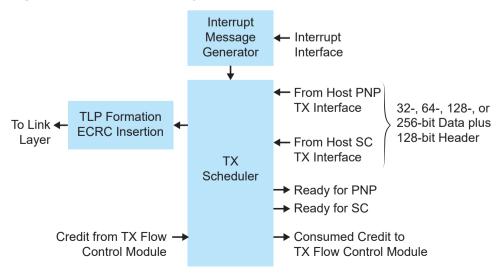

The TX side of the transaction layer receives data from the client logic through separate interfaces for each type (posted/non-posted and completion). A state machine processes the data, schedules the packets, and forwards them over a common data path to the data link layer.

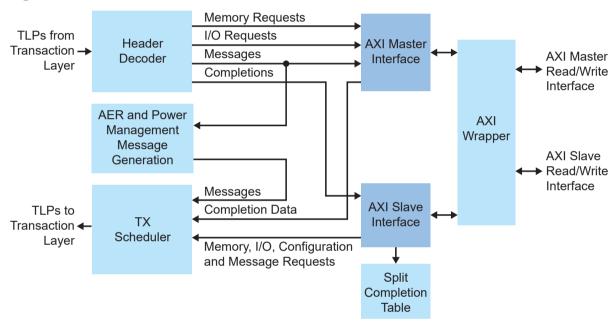

### **AXI Application Layer**

The application layer provides a simple interface to a host bus or DMA engine on the user side. The application layer has three separate interfaces to the user logic:

- Target memory read/write interface—Provides a straightforward interface to the user memory controller or DMA engine. This interface also delivers I/O requests and messages received from the link to the client. EPs need this interface.

- Master read/write interface—Lets an EP generate memory transactions to the host as bus master; an RP can generate memory, I/O, configuration, and message requests.

Devices that require bus master capability need this interface, e.g., all RPs and EPs that have master capability.

- Interrupt interface—Communicates the interrupt state between the user application and the PCIe Controller.

The application interface can maintain the state of up to 256 non-posted transactions (memory reads, I/O reads and writes, configuration reads and writes) generated on the master side, allowing their completions to be matched to the requests.

### **PCIe Controller Configuration**

Many of the PCIe Controller's interfaces and features are user configurable with the Efinity Interface Designer. The settings you make in the Interface Designer are the defaults that the PCIe Controller uses when you power it up or perform a cold reset. You can also change many of the settings via the APB interface (if you enable it).

**Learn more:** Refer to the **TJ-Series Interfaces User Guide** for a complete description of the settings you can configure with the Interface Designer.

# **Physical Layer**

Data arrives from the PIPE interface over one or more lanes. Each lane has a 32-bit interface and a clock frequency of 62, 125, 250, or 500 MHz depending on the link speed. The data flow happens as follows:

- 1. The data is converted to the core clock domain.

- 2. The PCle Controller de-scrambles each lane's data independently.

- **3.** Logic checks the data to detect any link power state transitions.

- **4.** Tthe lanes are de-skewed using FIFOs that are aligned on SKP sequences. The lanes are aligned as a single unit.

Figure 4: RX PHY Layer

A frame decoder decodes the de-skewed data, removes the SOP/EOP framing delimiters from the packet, and aligns them on the internal data path. The frame decoder can handle varying link widths and all potential packet alignments on the lanes. The decoded data is sent to the data link layer with indicators for packet type and errors detected.

The PCIe Controller sends each lane's received data to the Link Training Receive State Machine, which detects and decodes any training sequences from the lane. Each state machine passes information extracted from the training sequences to the LTSSM.

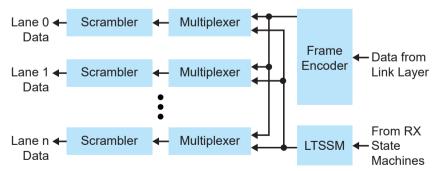

On the TX side, data arrives from the data link layer over a 128-bit data path, plus sideband signals. A frame decoder adds SOP and EOP delimiters to the packets and aligns them on the lanes. The frame encoder can handle varying link widths and all legal packet alignments on the lanes.

Figure 5: TX PHY Layer

The PCIe Controller multiplexes outgoing packets from the frame encoder with training sequences generated by the LTSSM. The multiplexer disables the data path from the frame encoder during link training, and allows the LTSSM to control the lanes. Each lane has its own scrambler to scramble the data before sending it to the PIPE interface. The outgoing PIPE interface has 32 bits per lane for all speeds with a PIPE clock frequency of 62, 125, 250, or 500 MHz), which determines the link speed.

### **SRIS Operation**

The PCIe Controller supports the Separate Reference Clock Independent Spread Spectrum (SRIS) ECN. With SRIS enabled, the PCIe Controller is in SRIS mode upon power-up and can transmit and receive the SKP ordered set (OS) as required by the SRIS specifications.

**Note:** The SRIS feature enables a higher clock tolerance from 600 ppm to 5,600 ppm in a separate reference clock configuration. Using an incompatible clock tolerance in your system may result in an unstable L0 state or packet timeout issues. Refer to the PCIe Base Specification 3.0 or higher for more information.

In SRIS mode, the PCIe Controller transmits SKP OS (as per the SRIS and PCIe 3.0 specifications) as follows:

- In 8b/10b encoding mode, the PCIe Controller transmits SKP OS every 128 symbols.

If, due to a transmission of a large TLP, the SKP OS cannot be sent at the 128 symbol boundary, the controller accumulates all SKP OS and sends them at the end of the TLP.

- In 128/130b encoding mode, the PCIe Controller transmits SKP OS every 32 blocks.

If, due to a transmission of a large TLP, the SKP OS cannot be sent at the 32 block boundary, the controller accumulates the SKP OS and send them at the end of the TLP.

On the RX side, the PCIe Controller can handle the higher frequency SKP OS reception as mandated by the SRIS specifications.

When SRIS mode is enabled, the following two features (as defined in the PCIe 3.0 specification) are changed:

- L0s capability is not advertised by the core in the link control register in PCI Express capability structure in the PCI compatible configuration space.

- The modified compliance pattern at 8G or higher is different. See the SRIS ECN specification for further details.

When the SRIS control register power-on default value is changed, the L0s capability in the Link Control register should be updated accordingly via the Local Management/APB interface.

The SRIS specification has an optional feature called Lower SKP OS generation/reception. The PCIe Controller implements this feature. With this feature, the PCIe device (if needed) can revert to the non-SRIS frequency of SKP OS generation when the PCIe link is in the L0 mode. This capability is advertised in the Lower SKP OS Generation/Reception Supported Speeds Vector field of the Link Capabilities 2 register. This feature is enabled/disabled using the Enable Lower SKP OS Generation Vector field of the Link Control 3 register.

When the SRIS feature is disabled using the SRIS control register, the Lower SKP OS Generation/Reception Supported Speeds Vector field of the Link Capabilities 2 register is disabled by forcing setting the value to zero.

Note: You can enable SRIS in the Interface Designer (PCI Express block > Base tab > SRIS Enable).

During operation, you can update the setting using the APB interface. As a control and debug feature, you can enable/ disable the SRIS feature using a control register in the local management space (refer to "SRIS Control Register" in the "Local Management Registers" chapter of the TJ-Series PCle Controller Registers User Guide). If you want to enable/disable SRIS mode, set/reset the SRIS Enable register field before link training begins.

Important: You cannot enable SRIS if active state power management (ASPM) is enabled.

# **RX Lane Margining**

The Receiver lane margining enables system software to obtain the receiver's margin information while the link is in L0 state. The PCIe Controller:

- Supports RX lane margining for timing and voltage in either direction from the current RX position.

- Supports RX lane margining in endpoint and root port modes.

- Supports RX lane margining for PHYs that implement an independent error sampler. (i.e., MIndErrorSampler ==1). MIndErrorSampler==0 is not supported.

- Supports all lanes being margined simultaneously.

- Supports PIPE interface revision 4.4.1 for margining.

- Implements programmable registers in the local management space for all PHY parameters related to margining.

- Implements the Lane Margining Capability Register Set in the PF0 configuration space at address offset 12'h920.

- Implements logic to detect and report invalid margining commands received from host software and the PHY.

Lane margining is driven by software. Software uses the Lane Margin Control and Status register in each port (downstream or upstream) for margin control and to obtain status information for the corresponding RX associated with the port.

When the host writes a new margining command to the Lane Margin Control Register, the PCIe Controller decodes the command and performs two checks to determine whether the command is:

- Valid:

- Commands that do not match defined command formats are treated as invalid.

- If the received command is invalid, the PCIe Controller discards the command and reports the error in LM register.

- Supported (step margin commands):

- Checks if the step margin offset is within the range supported by the device.

- If a step margin command is unsupported, the PCIe Controller responds with NAK status in the Lane Margin Status Register. An error is not flagged in the LM registers.

Note: Refer to Exception Handling on page 19 for more information on these checks.

The PCIe Controller then processes commands that are valid and supported. The PCIe Controller internally executes commands that do not require any action from the PHY, such as report commands. All other commands are delivered to the PHY over the PIPE interface.

The PCIe Controller responds to the host by updating the status appropriately in the Lane Margin Status Register. The register format is:

Table 2: Margining Lane Control and Status Register (i\_margining\_lane\_control\_status\_regX)

| [31:24]                     | [23]     | [22]                     | [21:19]               | [18:16]             | [15:8]            | [7]      | [6]            | [5:3]          | [2:0]     |

|-----------------------------|----------|--------------------------|-----------------------|---------------------|-------------------|----------|----------------|----------------|-----------|

| MPSTS                       | R1       | UMSTS                    | MTSTS                 | RNSTS               | MRGPAY            | R0       | USGMOD         | MRGTYP         | RCVNUM    |

| Margin<br>Payload<br>Status | Reserved | Usage<br>Model<br>Status | Margin<br>Type Status | RX Number<br>Status | Margin<br>Payload | Reserved | Usage<br>Model | Margin<br>Type | RX Number |

# **Command Processing (Endpoint)**

The following table shows how the PCIe Controller processes margining commands in endpoint mode.

**Table 3: Margining Command Processing in Endpoint Mode**

| Command (Margin Control Register)  | PIPE Interface | Response (Margin Status Register)                                                                                           |

|------------------------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------|

| No Command                         | No change      | Margin Type [2:0]: 111b                                                                                                     |

| Margin Type [2:0]: 111b            |                | Receiver Number [2:0]: 000b                                                                                                 |

| Receiver Number [2:0]: 000b        |                | Margin Payload [7:0]: 9Ch                                                                                                   |

| Margin Payload [7:0]: 9Ch          |                |                                                                                                                             |

| Access Retimer Register            | No change      | Invalid command for EP. Reported as an                                                                                      |

| Margin Type [2:0]: 001b            |                | invalid command in LM register.                                                                                             |

| Receiver Number [2:0]: 010b/100b   |                |                                                                                                                             |

| Margin Payload [7:0]: XXh          |                |                                                                                                                             |

| Report Margin Control Capabilities | No change      | Margin Type [2:0]: 001b                                                                                                     |

| Margin Type [2:0]: 001b            |                | Receiver Number [2:0]: 110b                                                                                                 |

| Receiver Number [2:0]: 110b        |                | Margin Payload [7:5]: 000b                                                                                                  |

| Margin Payload [7:0]: 88h          |                | Margin Payload [4:0]: {MIndErrorSampler, MSampleReportingMethod, MIndLeftRightTiming, MIndUpDownVoltage, MVoltageSupported} |

| Report MNumVoltageSteps            | No change      | Margin Type [2:0]: 001b                                                                                                     |

| Margin Type [2:0]: 001b            |                | Receiver Number [2:0]: 110b                                                                                                 |

| Receiver Number [2:0]: 110b        |                | Margin Payload [7]: 0                                                                                                       |

| Margin Payload [7:0]: 89h          |                | Margin Payload [6:0]: MNumVoltageSteps                                                                                      |

| Report MNumTimingSteps             | No change      | Margin Type [2:0]: 001b                                                                                                     |

| Margin Type [2:0]: 001b            |                | Receiver Number [2:0]: 110b                                                                                                 |

| Receiver Number [2:0]: 110b        |                | Margin Payload [7:6]: 00                                                                                                    |

| Margin Payload [7:0]: 8Ah          |                | Margin Payload [5:0]: MNumTimingSteps                                                                                       |

| Report MMaxTimingOffset            | No change      | Margin Type [2:0]: 001b                                                                                                     |

| Margin Type [2:0]: 001b            |                | Receiver Number [2:0]: 110b                                                                                                 |

| Receiver Number [2:0]: 110b        |                | Margin Payload [7]: 0                                                                                                       |

| Margin Payload [7:0]: 8Bh          |                | Margin Payload [6:0]: MMaxTimingOffset                                                                                      |

| Report MMaxVoltageOffset           | No change      | Margin Type [2:0]: 001b                                                                                                     |

| Margin Type [2:0]: 001b            |                | Receiver Number [2:0]: 110b                                                                                                 |

| Receiver Number [2:0]: 110b        |                | Margin Payload [7]: 0                                                                                                       |

| Margin Payload [7:0]: 8Ch          |                | Margin Payload [6:0]: MMaxVoltageOffset                                                                                     |

| Report MSamplingRateVoltage        | No change      | Margin Type [2:0]: 001b                                                                                                     |

| Margin Type [2:0]: 001b            |                | Receiver Number [2:0]: 110b                                                                                                 |

| Receiver Number [2:0]: 110b        |                | Margin Payload [7:6]: 00                                                                                                    |

| Margin Payload [7:0]: 8Dh          |                | Margin Payload [5:0]                                                                                                        |

|                                    |                | = {MSamplingRateVoltage [5:0]}                                                                                              |

| Report MSamplingRateTiming         | No change      | Margin Type [2:0]: 001b                                                                                                     |

| Margin Type [2:0]: 001b            |                | Receiver Number [2:0]: 110b                                                                                                 |

| Receiver Number [2:0]: 110b        |                | Margin Payload [7:6]: 00                                                                                                    |

| Margin Payload [7:0]: 8Eh          |                | Margin Payload [5:0]: {MSamplingRateTiming [5:0]}                                                                           |

| ReportMSampleCount                 | No change      | Margin Type [2:0]: 001b                                                                                                     |

| Margin Type [2:0]: 001b            |                | Receiver Number [2:0]: 110b                                                                                                 |

| Receiver Number [2:0]: 110b        |                | Margin Payload [7]: 0                                                                                                       |

| Margin Payload [7:0]: 8Fh          |                | Margin Payload [6:0]: MSampleCount                                                                                          |

| Command (Margin Control Register)                                                                                                           | PIPE Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Response (Margin Status Register)                                                                                                                                                                                                                                                                                                                                                          |

|---------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ReportMMaxLanes Margin Type [2:0]: 001b Receiver Number [2:0]: 110b Margin Payload [7:0]: 90h                                               | No change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Margin Type [2:0]: 001b<br>Receiver Number [2:0]: 110b<br>Margin Payload [7:5]: 00<br>Margin Payload [6:0]: MMaxLane                                                                                                                                                                                                                                                                       |

| Set Error Count Limit Margin Type [2:0]: 010b Receiver Number [2:0]: 110b Margin Payload [7:6]: 11b Margin Payload [5:0]: Error Count Limit | No change Register Error Limit [5:0] in the Local Management Register in the core clock domain.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Margin Payload [7:6]: 11b  Margin Payload [5:0]: Error Count  Limit registered by the target receiver                                                                                                                                                                                                                                                                                      |

| Go to Normal Settings Margin Type [2:0]: 010b Receiver Number [2:0]: 000b or 110b Margin Payload [7:0]: 0Fh                                 | <ul> <li>Write committed to RX Margin Control 0 with Start Margin = 0.</li> <li>Wait for Write Ack response from PHY or a 10 ms timeout.</li> <li>Wait for PHY2MAC write committed to Margin Status or a 10 ms timeout.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Margin Type [2:0]: 010b<br>Receiver Number [2:0]: 110b<br>Margin Payload [7:0]: 0Fh                                                                                                                                                                                                                                                                                                        |

| Clear Error Log Margin Type [2:0]: 010b Receiver Number [2:0]: 000b or 110b Margin Payload [7:0]: 55h                                       | <ul> <li>Write committed to RX Margin Control 0 with Error Count Reset = 1. Other fields picked up from the RX Margin Control 0 Mirror Register.</li> <li>Wait for Write Ack response from PHY or a 10 ms timeout.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Margin Type [2:0]: 010b<br>Receiver Number [2:0]: 110b<br>Margin Payload [7:0]: 55h                                                                                                                                                                                                                                                                                                        |

| Step Margin to Timing Offset to Right/Left of Default Margin Type [2:0]: 011b Receiver Number [2:0]: 110b Margin Payload [7:0]: XX          | If a step margin to voltage is already in progress or if a step margin to timing in the opposite direction is in progress:  Stop margining by issuing write committed to RX Margin Control 0 with Start Margin = 0.  Other fields picked up from the RX Margin Control 0 Mirror Register.  Wait for Write Ack response from PHY or a 10 ms timeout.  Wait for PHY2MAC Write Committed to Margin Status or a 10 ms timeout.  Check if RX margin command is supported.  If margin offset is supported:  Issue Write Uncommitted to RX Margin Control 1 with Margin Offset [6:0] = Margin Payload [5:0].  Issue Write Committed to RX Margin Control 0 with StartMargin: 1 and MarginTiming: 1.  Wait for Write Ack response from PHY or a 10ms timeout.  Wait for PHY2MAC Write Committed to Margin Status or a 10 ms timeout.  Otherwise:  Issue NAK Status and exit. | Margin Type [2:0]: 011b Receiver Number [2:0]: 110b IF (Unsupported Range in Command) Margin Payload [7:6]: 11 ELSIF (Write ACK received for Margin Command) Margin Payload [7:6]: 01 ELSIF (PIPE MAC RX Margin Register 0 Margin Status) Margin Payload [7:6]: 10 ELSIF (Error Count > Limit) Margin Payload [7:6]: 00 Margin Payload [5:0]: Error Count from RX Margin Status 2 Register |

| Command (Margin Control Register)                                                                                                       | PIPE Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Response (Margin Status Register)                                                                                                                                                                                                                                                                                                                                                          |

|-----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Step Margin to Voltage Offset to Up/<br>Down of Default  Margin Type [2:0]: 100b  Receiver Number [2:0]: 110b  Margin Payload [7:0]: XX | If a step margin to timing is already in progress or if a step margin to voltage in the opposite direction is in progress:  Stop Margining by issuing Write Committed to RX Margin Control 0 with Start Margin = 0. Other fields picked up from the RX Margin Control 0 Mirror Register.  Wait for Write Ack response from PHY or a 10ms timeout.  Wait for PHY2MAC Write Committed to Margin Status or a 10 ms timeout.  Check if an RX margin command is valid.  If margin offset is supported:  Issue Write Uncommitted to RX Margin Control 1 with Margin Offset [6:0] = Margin Payload [6:0].  Issue Write Committed to RX Margin Control 0 with StartMargin: 1 and MarginVoltage: 1  Wait for Write Ack response from PHY or a 10ms timeout.  Wait for PHY2MAC Write Committed to Margin Status or a 10 ms timeout.  Otherwise:  Issue NAK Status and exit. | Margin Type [2:0]: 100b Receiver Number [2:0]: 110b IF (Unsupported Range in Command) Margin Payload [7:6]: 11 ELSIF (Write ACK received for Margin Command) Margin Payload [7:6]: 01 ELSIF (PIPE MAC RX Margin Register 0 Margin Status) Margin Payload [7:6]: 10 ELSIF (Error Count > Limit) Margin Payload [7:6]: 00 Margin Payload [5:0]: Error Count from RX Margin Status 2 Register |

| Vendor Defined  Margin Type [2:0]: 101b  Receiver Number [2:0]: 110b  Margin Payload [7:0]: Vendor  Defined                             | No change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Margin Type [2:0]: 101b Receiver Number [2:0]: 110b Margin Payload [7:0]: Vendor Defined Margin Payload status same as received in control register.                                                                                                                                                                                                                                       |

# **Command Processing (Root Port)**

The following table shows how the PCIe Controller processes margining commands in root port mode.

**Table 4: Command Processing in Roor Port Mode**

| Command (Margin<br>Control Register)            | PIPE Interface | Response (Margin Status Register)                                |

|-------------------------------------------------|----------------|------------------------------------------------------------------|

| No Command                                      | No change      | Margin Type [2:0]: 111b                                          |

| Margin Type [2:0]: 111b                         |                | Receiver Number [2:0]: 000b                                      |

| Receiver Number [2:0]: 000b                     |                | Margin Payload [7:0]: 9Ch                                        |

| Margin Payload [7:0]: 9Ch                       |                |                                                                  |

| Access Retimer Register Margin Type [2:0]: 001b | No change      | Command sent on Control SKP sent by downstream port.             |

| Receiver Number [2:0]: 010b/100b                |                | Margin Status Updated from the Control                           |

| Margin Payload [7:0]: XXh                       |                | SKP OS received by the downstream port.                          |

| Report Margin Control                           | No change      | Margin Type [2:0]: 001b                                          |

| Capabilities                                    |                | Receiver Number [2:0]: 001b                                      |

| Margin Type [2:0]: 001b                         |                | Margin Payload [7:5]: 000b                                       |

| Receiver Number [2:0]: 001b through 101b        |                | Margin Payload [4:0]: {MIndErrorSampler, MSampleReportingMethod, |

| Margin Payload [7:0]: 88h                       |                | MIndLeftRightTiming, MIndUpDownVoltage, MVoltageSupported}       |

| Command (Margin<br>Control Register)                                                                                                                     | PIPE Interface                                                                                                                                                                                                                     | Response (Margin Status Register)                                                                                                                       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| Report MNumVoltageSteps Margin Type [2:0]: 001b Receiver Number [2:0]: 001b through 101b Margin Payload [7:0]: 89h                                       | No change                                                                                                                                                                                                                          | Margin Type [2:0]: 001b<br>Receiver Number [2:0]: 001b<br>Margin Payload [7]: 0<br>Margin Payload [6:0]: MNumVoltageSteps                               |

| Report MNumTimingSteps Margin Type [2:0]: 001b Receiver Number [2:0]: 001b Margin Payload [7:0]: 8Ah                                                     | No change                                                                                                                                                                                                                          | Margin Type [2:0]: 001b Receiver Number [2:0]: 001b Margin Payload [7:6]: 00 Margin Payload [5:0]: MNumTimingSteps                                      |

| Report MMaxTimingOffset Margin Type [2:0]: 001b Receiver Number [2:0]: 001b through 101b Margin Payload [7:0]: 8Bh                                       | No change                                                                                                                                                                                                                          | Margin Type [2:0]: 001b Receiver Number [2:0]: 001b Margin Payload [7]: 0 Margin Payload [6:0]: MMaxTimingOffset                                        |

| Report MMaxVoltageOffset Margin Type [2:0]: 001b Receiver Number [2:0]: 001b through 101b Margin Payload [7:0]: 8Ch                                      | No change                                                                                                                                                                                                                          | Margin Type [2:0]: 001b Receiver Number [2:0]: 001b Margin Payload [7]: 0 Margin Payload [6:0]: MMaxVoltageOffset                                       |

| Report MSamplingRateVoltage Margin Type [2:0]: 001b Receiver Number [2:0]: 001b through 101b Margin Payload [7:0]: 8Dh                                   | No change                                                                                                                                                                                                                          | Margin Type [2:0]: 001b Receiver Number [2:0]: 001b Margin Payload [7:6]: 00 Margin Payload [5:0]: {MSamplingRateVoltage [5:0]}                         |

| Report MSamplingRateTiming Margin Type [2:0]: 001b Receiver Number [2:0]: 001b through 101b Margin Payload [7:0]: 8Eh                                    | No change                                                                                                                                                                                                                          | Margin Type [2:0]: 001b Receiver Number [2:0]: 001b Margin Payload [7:6]: 00 Margin Payload [5:0]: {MSamplingRateTiming [5:0]}                          |

| ReportMSampleCount Margin Type [2:0]: 001b Receiver Number [2:0]: 001b through 101b Margin Payload [7:0]: 8Fh                                            | No change                                                                                                                                                                                                                          | Margin Type [2:0]: 001b Receiver Number [2:0]: 001b Margin Payload [7]: 0 Margin Payload [6:0]: MSampleCount                                            |

| ReportMMaxLanes Margin Type [2:0]: 001b Receiver Number [2:0]: 001b through 101b Margin Payload [7:0]: 90h                                               | No change                                                                                                                                                                                                                          | Margin Type [2:0]: 001b<br>Receiver Number [2:0]: 001b<br>Margin Payload [7:5]: 00<br>Margin Payload [6:0]: MMaxLane                                    |

| Set Error Count Limit Margin Type [2:0]: 010b Receiver Number [2:0]: 001b through 101b Margin Payload [7:6]: 11b Margin Payload [5:0]: Error Count Limit | No change                                                                                                                                                                                                                          | Margin Type [2:0]: 001b Receiver Number [2:0]: 001b Margin Payload [7:6]: 11b Margin Payload [5:0]: Error Count Limit registered by the target Receiver |

| Go to Normal Settings Margin Type [2:0]: 010b Receiver Number [2:0]: 000b through 101b Margin Payload [7:0]: 0Fh                                         | <ul> <li>Write Committed to RX Margin Control 0 with Start Margin = 0.</li> <li>Wait for Write Ack response from PHY or a 10 ms timeout.</li> <li>Wait for PHY2MAC Write Committed to Margin Status or a 10 ms timeout.</li> </ul> | Margin Type [2:0]: 010b<br>Receiver Number [2:0]: 001b<br>Margin Payload [7:0]: 0Fh                                                                     |

| Command (Margin<br>Control Register)                                                                                                               | PIPE Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Response (Margin Status Register)                                                                                                                                                                                                                                                                                                                                                          |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Clear Error Log<br>Margin Type [2:0]: 010b<br>Receiver Number [2:0]: 000b<br>through 101b<br>Margin Payload [7:0]: 55h                             | <ul> <li>Write Committed to RX Margin Control 0         with Error Count Reset = 1. Other fields         picked up from the RX Margin Control 0         Mirror Register.</li> <li>Wait for Write Ack response from PHY or a         10 ms timeout.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Margin Type [2:0]: 010b<br>Receiver Number [2:0]: 001b<br>Margin Payload [7:0]: 55h                                                                                                                                                                                                                                                                                                        |  |  |

| Step Margin to Timing Offset to Right/Left of Default  Margin Type [2:0]: 011b  Receiver Number [2:0]: 001b through 101b  Margin Payload [7:0]: XX | If a step margin to voltage is already in progress or if a step margin to timing in the opposite direction is in progress:  Stop Margining by issuing Write Committed to RX Margin Control 0 with Start Margin = 0. Other fields picked up from the RX Margin Control 0 Mirror Register.  Wait for Write Ack response from PHY or a 10 ms timeout.  Wait for PHY2MAC Write Committed to Margin Status or a 10 ms timeout.  Check if RX margin command is supported.  If margin offset is supported:  Issue Write Uncommitted to RX Margin Control 1 with Margin Offset [6:0] = Margin Payload [5:0].  Issue Write Committed to RX Margin Control 0 with StartMargin: 1 and MarginTiming: 1.  Wait for Write Ack response from PHY or a 10 ms timeout.  Wait for PHY2MAC Write Committed to Margin Status or a 10 ms timeout.  Otherwise:  Issue NAK Status and exit. | Margin Type [2:0]: 011b Receiver Number [2:0]: 001b IF (Unsupported Range in Command) Margin Payload [7:6]: 11 ELSIF (Write ACK received for Margin Command) Margin Payload [7:6]: 01 ELSIF (PIPE MAC RX Margin Register 0 Margin Status) Margin Payload [7:6]: 10 ELSIF (Error Count > Limit) Margin Payload [7:6]: 00 Margin Payload [5:0]: Error Count from RX Margin Status 2 Register |  |  |

| Step Margin to Voltage Offset to Up/Down of Default  Margin Type [2:0]: 100b  Receiver Number [2:0]: 001b through 110b  Margin Payload [7:0]: XX   | If a step margin to timing is already in progress or if a step margin to voltage in the opposite direction is in progress:  Stop Margining by issuing Write Committed to RX Margin Control 0 with Start Margin = 0. Other fields picked up from the RX Margin Control 0 Mirror Register.  Wait for Write Ack response from PHY or a 10 ms timeout.  Wait for PHY2MAC Write Committed to Margin Status or a 10 ms timeout.  Check if RX margin command is valid.  If margin offset is supported: Issue Write Uncommitted to RX Margin Control 1 with Margin Offset [6:0] = Margin Payload [6:0]. Issue Write Committed to RX Margin Control 0 with StartMargin: 1 and MarginVoltage: 1 Wait for Write Ack response from PHY or a 10 ms timeout. Wait for PHY2MAC Write Committed to Margin Status or a 10 ms timeout. Otherwsie: Issue NAK Status and exit.           | Margin Type [2:0]: 100b Receiver Number [2:0]: 001b IF (Unsupported Range in Command) Margin Payload [7:6]: 11 ELSIF (Write ACK received for Margin Command) Margin Payload [7:6]: 01 ELSIF (PIPE MAC RX Margin Register 0 Margin Status) Margin Payload [7:6]: 10 ELSIF (Error Count > Limit) Margin Payload [7:6]: 00 Margin Payload [5:0]: Error Count from RX Margin Status 2 Register |  |  |

| Vendor Defined Margin Type [2:0]: 101b Receiver Number [2:0]: 001b Margin Payload [7:0]: Vendor Defined                                            | No change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Margin Type [2:0]: 101b Receiver Number [2:0]: 001b Margin Payload [7:0]: Vendor Defined Margin Payload status same as received in control register.                                                                                                                                                                                                                                       |  |  |

### **Step Margin Command Execution**

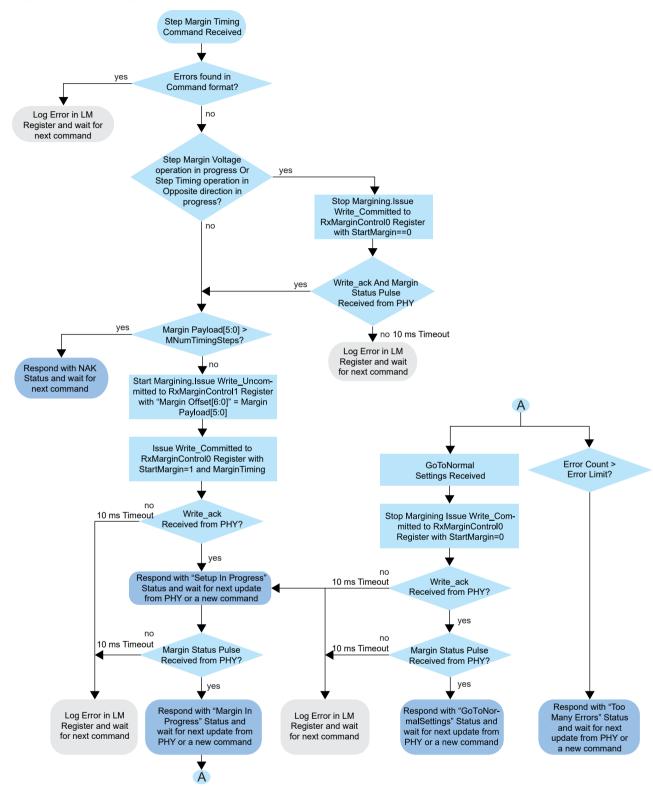

Figure 6: Step Margin for Timing Command Execution

Step Margin Voltage Command Received Errors found in ves Command format? Log Error in LM no Register and wait for next command Step Margin Timing operation in progress Or Step Voltage operation in Opposite direction in Stop Margining.Issue Write\_Committed to progress? RxMarginControl0 Register with StartMargin==0 Write\_ack And Margin yes Status Pulse Received from PHY Margin Payload[6:0] > MNumTimingSteps no 10 ms Timeout Log Error in LM **→** no Register and wait Respond with NAK for next command Start Margining.Issue Write\_Uncommitted to RxMarginControl1 Register Status and wait for next command with "Margin Offset[6:0]" = Margin Payload[6:0] Issue Write\_Committed to Error Count > RxMarginControl0 Register with GoToNormalSettings StartMargin=1 and MarginVoltage Error Limit Received 10 ms Timeout Write\_ack Stop Margining Issue Write\_Com-Received from PHY mitted to RxMarginControl0 Register with StartMargin=0 Respond with "Setup In Progress" Status and wait for next update from PHY or a new command. no 10 ms Timeout Write\_ack Received from PHY yes 10 ms Timeout Margin Status Pulse 10 ms Timeout Margin Status Pulse Received from PHY Received from PHY yes Respond with "Too Many Errors" Status Respond with "GoToNor-malSettings" Status and Respond with "Margin In Log Error in LM Log Error in LM Progress" Status and Register and wait and wait for next update from PHY or Register and wait wait for next update from wait for next update from for next command for next command PHY or a new command. PHY or a new command. a new command.

Figure 7: Step Margin for Voltage Command Execution

### **Step Margin Execution Status**

The step margin execution status is updated when a write committed is received from the PHY. The 2-bit status is derived as shown in the following table.

**Table 5: Step Margin Status**

| Inputs                                                                                                                                                                                         | Step Margin<br>Execution<br>Status [1:0] | Description                                                                                                                                                                                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PHY issues Write_Ack in response to a write committed by the PCIe Controller to start margining.                                                                                               | 01                                       | 01b: Set up for margin in progress. The receiver is getting ready but has not yet started executing the step margin command. MErrorCount is 0.                                                            |

| PHY sets the Margin Status bit in RX Margin Status 0 PIPE MAC Register in response to a write committed by the PCIe Controller to start margining.                                             | 10                                       | 10b: Margining in progress. The receiver is executing the step margin command. MErrorCount reflects the number of errors detected.                                                                        |

| PHY sets the margin NAK bit in the RX Margin Status 0 PIPE MAC Register in response to a write committed by the PCIe Controller to start margining.                                            | 11                                       | 11b: NAK. Indicates that an unsupported lane margining command was issued. For example, timing margin beyond +/- 0.2 UI. MErrorCount is 0.                                                                |

| PHY updates error count bits [5:0] by issuing a write committed to the MAC RX Margin Status 2 Register. When error count bits [5:0] is greater than error limit[5:0], update execution status. | 00                                       | 00b: Too many errors. The receiver autonomously went back to its default settings. MErrorCount reflects the number of errors detected. Note that MErrorCount might be greater than the error count limit. |

# **Control SKIP for Lane Margining at Receiver**

The Step Margin Execution Status is updated when write committed is received from the PHY. The 2-bit status is derived as shown in the following tables.

**Table 6: Control SKP Ordered Set Format**

Where *N* is 1 - 5.

| Symbol Number       | Value  | Description                                                                                                                          |

|---------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------|

| 0 through (4*N - 1) | AAh    | SKP Symbol. Symbol 0 is the SKP Ordered Set identifier.                                                                              |

| 4*N                 | 78h    | SKP_END_CTL Symbol. Signifies the end of the Control SKP Ordered Set after three more symbols.                                       |

| 4*N + 1             | 00-FFh | Bit 7: Data Parity Bit 6: First Retimer Data Parity Bit 5: Second Retimer Parity Bits [4:0]: Margin CRC [4:0]                        |

| 4*N + 2             | 00-FFh | Bit 7: Margin Parity Bit 6: Usage Model : Set to 0b to indicate RX Lane Margining Bit [5:3]: Margin Type Bits [2:0]: Receiver Number |

| 4*N + 3             | 00-FFh | Bits [7:0] : Margin Payload                                                                                                          |

Table 7: Control SKP during Root Port and Endpoint Mode

| Types          | Root Port Mode                                                                                                                                                                                      | Endpoint Mode                                           |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|

| Control SKP TX | The contents of the four control fields of the Lane Margin Control and Status Register in the downstream port are always shown in the identical fields in the transmitted Control SKP Ordered Sets. | The Control SKIP is always transmitted with No Command. |

| Types          | Root Port Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Endpoint Mode                                                                                                                                                                                                                                           |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Control SKP RX | The PCIe Controller checks the Margin CRC and Margin Parity in the received Control SKIP Ordered Sets. Any mismatch detected is reported in the Lane Error Status Register.  The contents of the Control SKP Ordered Set received in the downstream port is reflected in the corresponding status fields of the Lane Margin Control and Status Register in the downstream port if either of these conditions are met in the Lane Margin Control and Status Register:  Receiver number is 010b - 101b.  Receiver number is 000b, margin command is clear, rrror log is no command or Go to Normal Settings, and there are retimer(s) in the link. | The PCIe Controller checks the margin CRC and margin parity in the received Control SKIP Ordered Sets. Detected mismatches are reported in the Lane Error Status Register.  The contents of the Control SKIP Ordered Sets are ignored in endpoint mode. |

### **Exception Handling**

When host software writes a command into the PCle Controller's Lane Margin Control Register, the PCle Controller performs a Command Valid Check and a Command Supported Check.

### **Command Valid Check**

The PCIe Controller checks for errors in the Margining Lane Control Register. Commands that do not match any defined formats are treated as invalid. If the host software writes an invalid command to the register, the PCIe Controller detects and reports the error in the Local Management Register Margining Error Status 1 Register.

The PCIe Controller logs the first error and sets the error status bit. The software must clear this status bit needs before another error can be logged. PCIe Controller continues to accept subsequent commands written by software in the Margining Lane Control Register regardless of previous errors.

**Table 8: Valid Commands for EndPoint Mode**

Any other commands are considered invalid.

| Margin Command          | Margin Type[2:0] | Receiver Number[2:0] | Margin Payload[7:0] |

|-------------------------|------------------|----------------------|---------------------|

| No Command              | 111              | 000                  | 9Ch                 |

| Report                  | 001              | 110                  | 88h to 90h          |

| SetErrorCountLimit      | 010              | 110                  | {11xx_xxxx}         |

| GoToNormalSettings      | 010              | 000, 110             | 0Fh                 |

| ClearErrorLog           | 010              | 000, 110             | 55h                 |

| StepMarginTimingOffset  | 011              | 110                  | {xxxx_xxxx}         |

| StepMarginVoltageOffset | 100              | 110                  | {xxxx_xxxx}         |

| VendorDefined           | 101              | 110                  | {xxxx_xxxx}         |

**Table 9: Valid Commands for Root Port Mode**

Any other commands are considered invalid.

| Margin Command          | Margin Type[2:0] | Receiver Number[2:0] | Margin Payload[7:0] |

|-------------------------|------------------|----------------------|---------------------|

| No Command              | 111              | 000                  | 9Ch                 |

| Access Retimer          | 001              | 010, 100             | {xxxx_xxxx}         |

| Report                  | 001              | 001 through 101      | 88h to 90h          |

| SetErrorCountLimit      | 010              | 001 through 101      | {11xx_xxxx}         |

| GoToNormalSettings      | 010              | 000 through 101      | 0Fh                 |

| ClearErrorLog           | 010              | 000 through 101      | 55h                 |

| StepMarginTimingOffset  | 011              | 001 through 101      | {xxxx_xxxx}         |

| StepMarginVoltageOffset | 100              | 001 through 101      | {xxxx_xxxx}         |

| Margin Command | Margin Type[2:0] | Receiver Number[2:0] | Margin Payload[7:0] |

|----------------|------------------|----------------------|---------------------|

| VendorDefined  | 101              | 001 through 101      | {xxxx_xxxx}         |

### **Command Supported Check**

The PCIe Controller performs this check for Step Margin commands. When it receives a valid Step Margin command, the PCIe Controller further checks whether the Step Margin Offset is within the supported range. If a Step Margin command is unsupported, the PCIe Controller responds with NAK status in the Lane Margin Status Register. No error is flagged in LM registers in this case.

- The Step Margin Timing check is: Check Margin Payload[5:0] <= MNumTimingSteps

- The Step Margin Voltage check is: Check Margin Payload[6:0] <= MNumVoltageSteps

### **RX Margining PIPE Interface: Write Ack Timeout**

During the execution of the GoToNormalSettings, ClearErrorLog, StepMarginTimingOffset or StepMarginVoltageOffset commands, the PCIe Controller issues a write committed command to the PHY over the PIPE interface and waits for the PHY to respond with WriteAck.

PCIe Controller waits for 10 ms to receive a WriteAck. If it is not received, the PCIe Controller reports an error in the Local Management Register Margining Error Status 2 Register.

### **Link Transition from Gen4 L0 State**

The PCIe Controller only accepts margining commands when the link is in Gen4 L0 state. After the command is accepted, the PCIe Controller continues processing the command as long as the link remains in the Gen4 L0 or Recovery states.

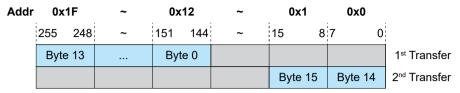

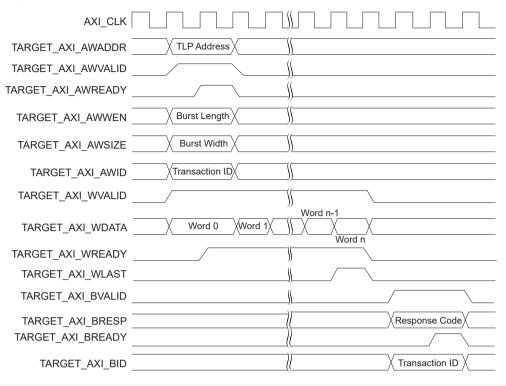

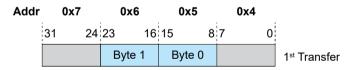

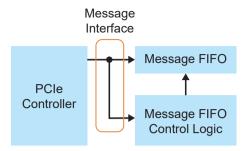

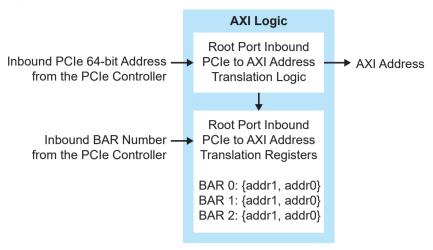

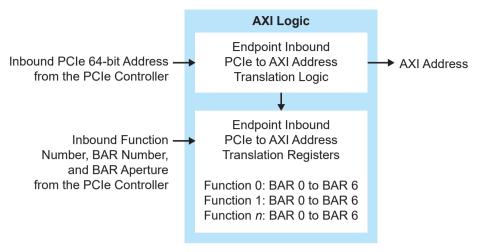

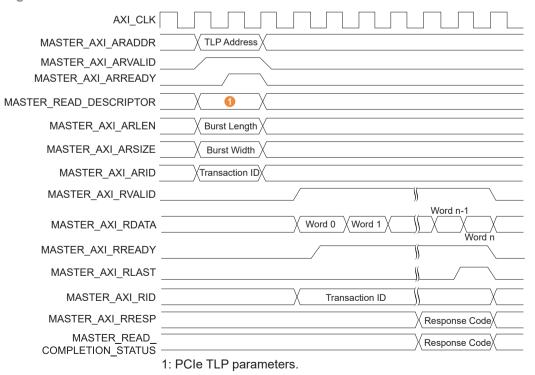

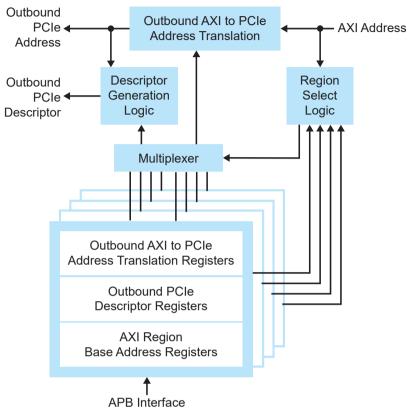

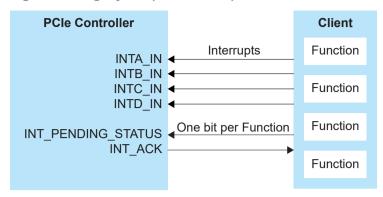

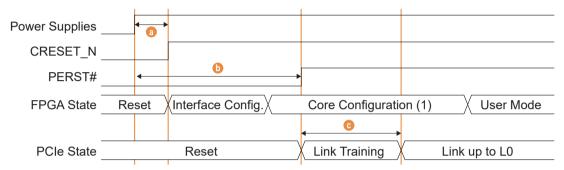

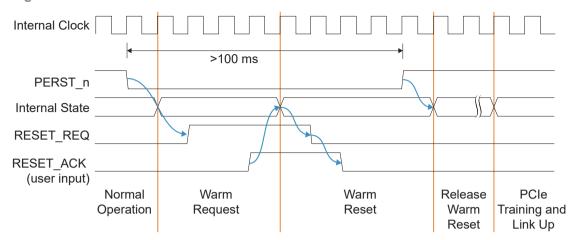

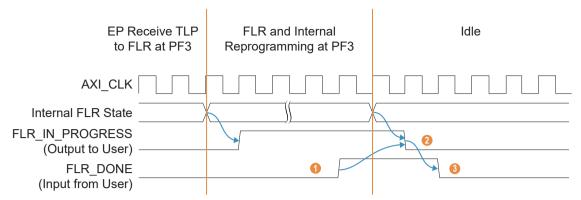

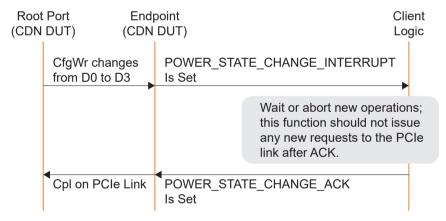

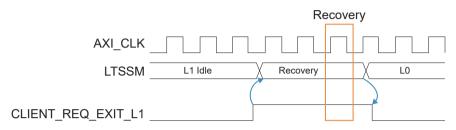

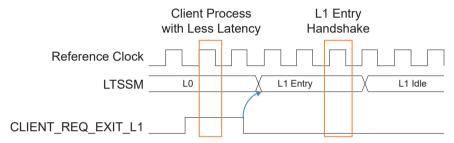

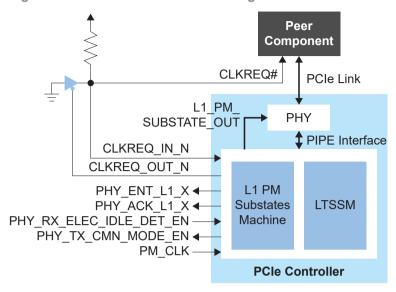

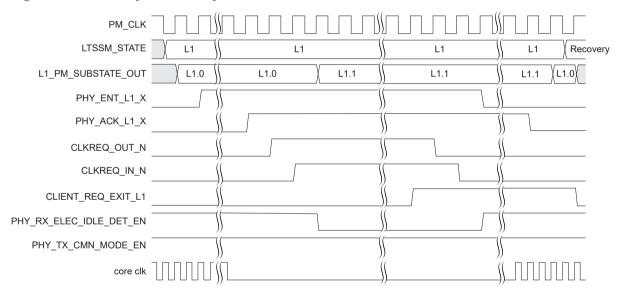

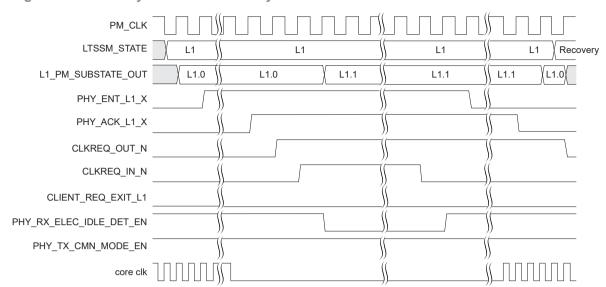

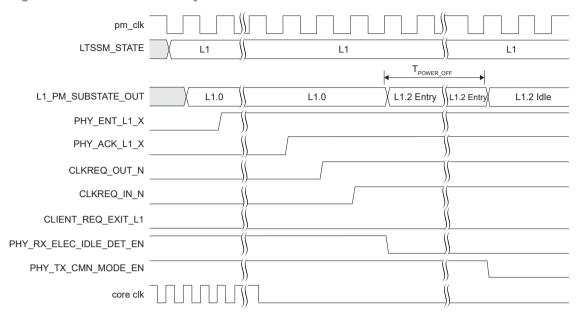

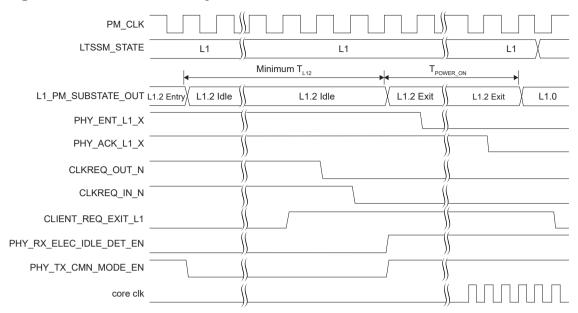

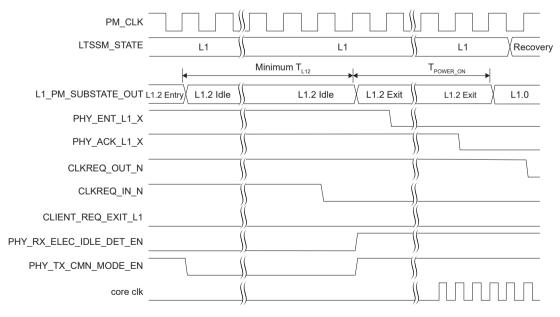

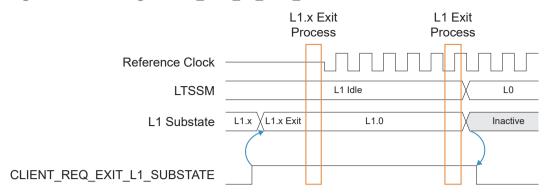

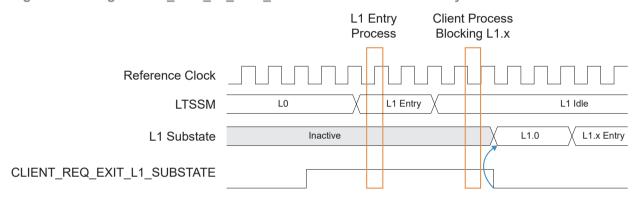

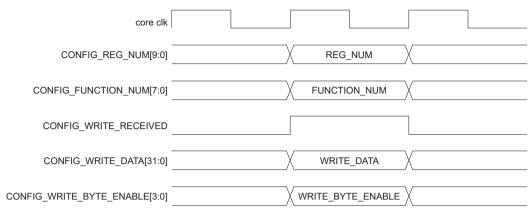

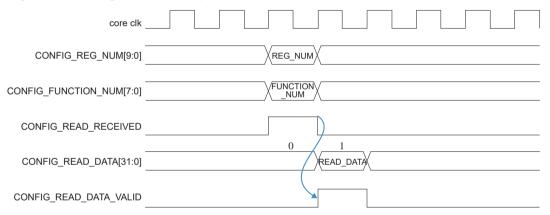

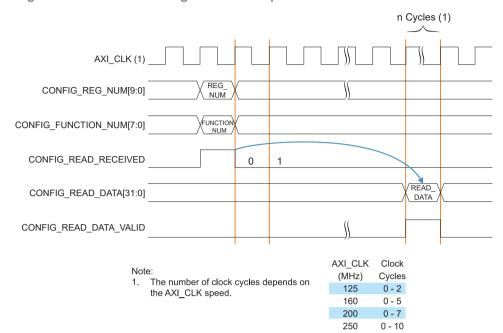

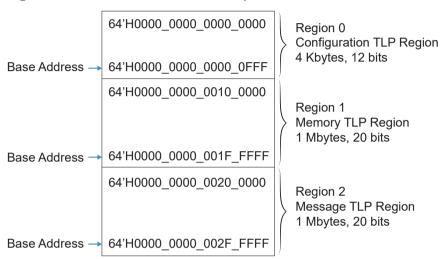

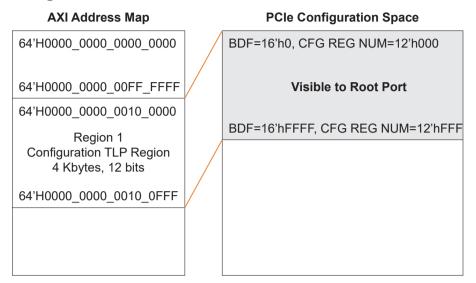

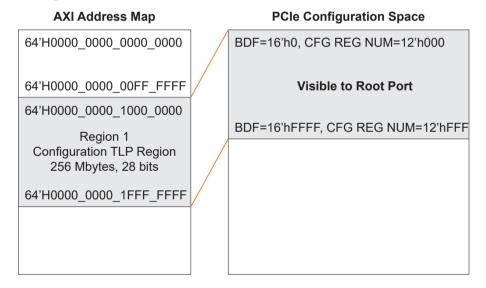

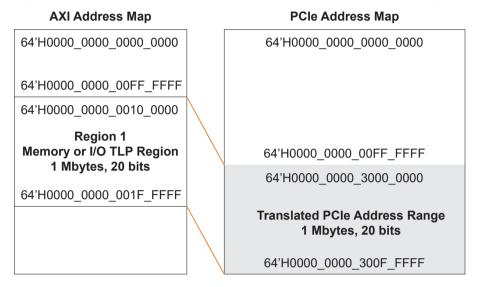

While a margining command is being processed, if the link transitions out of the Gen4 L0 or Recovery states, the PCIe Controller: