# User Guide

UG-SAPPHIREHPB-v3.0 November 2025 www.elitestek.com

# **Contents**

| Introduction                                            | v    |

|---------------------------------------------------------|------|

| Efinity <sup>®</sup> RISC-V Embedded Software IDE       |      |

| Required Software                                       |      |

| Required Hardware                                       |      |

| Comparison with Sapphire SoC                            |      |

| Performance                                             | VIII |

| Chapter 1: Install Software and SoC                     | 9    |

| Install the Efinity Software                            |      |

| Install the Efinity RISC-V Embedded Software IDE        | 9    |

| Chapter 2: IP Manager                                   |      |

| Customizing the Sapphire High-Performance SoC           |      |

| Modify the Bootloader                                   | 17   |

| Chapter 3: Recommended Design Practice                  | 19   |

| Chapter 4: Example Design                               | 21   |

| About the Example Design                                |      |

| Enable the LPDDR4x Memory (TJ375 N529 Board)            |      |

| Installing USB Drivers                                  |      |

| Program the Development Board                           | 24   |

| Chapter 5: Launch Efinity RISC-V Embedded Software IDE  | 25   |

| Launching the Efinity RISC-V Embedded Software IDE      |      |

| IDE Launcher from Efinity                               |      |

| Optimization Settings                                   |      |

| Chapter 6: Create, Import, and Build a Software Project | 32   |

| Create a New Project                                    |      |

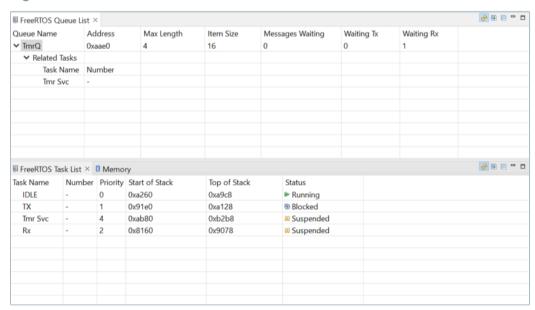

| Import Sample Projects                                  |      |

| Build                                                   | 39   |

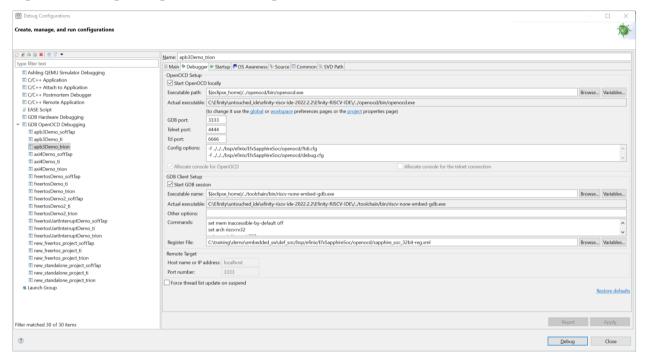

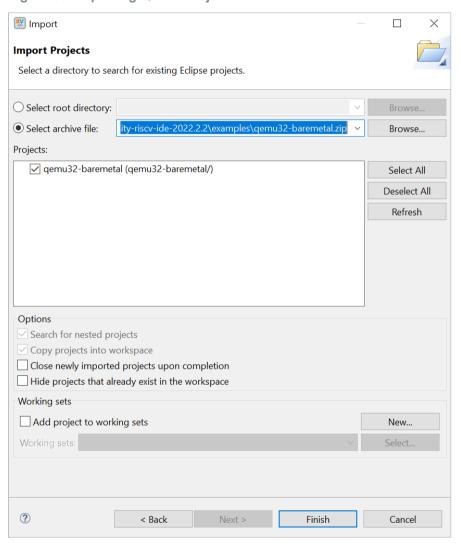

| Chapter 7: Debug with the OpenOCD Debugger              | 40   |

| Launch the Debug Script                                 |      |

| Debug                                                   |      |

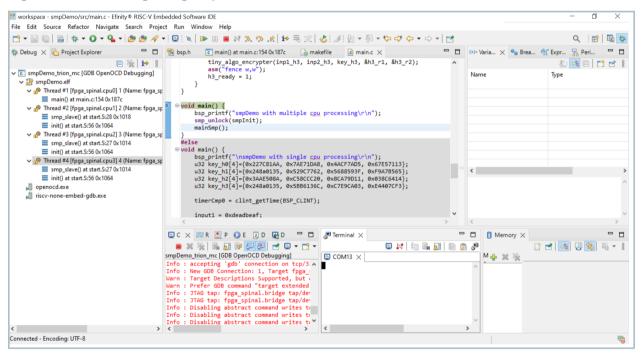

| Debug - Multiple Cores                                  | 43   |

| Debug - SMP                                             |      |

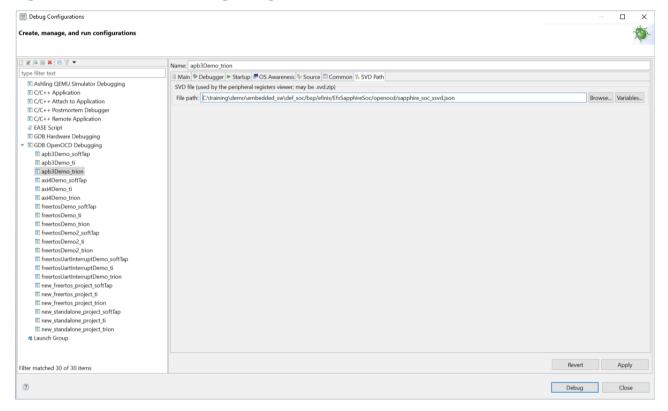

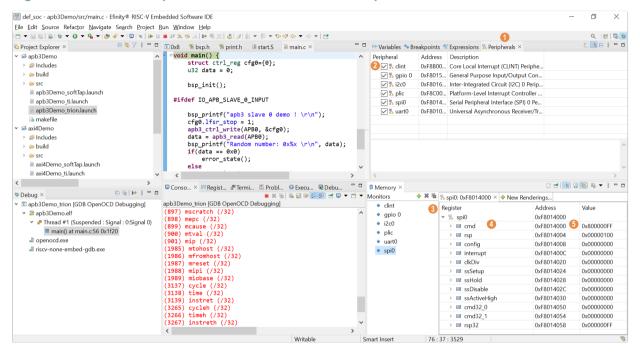

| Peripheral Register View                                |      |

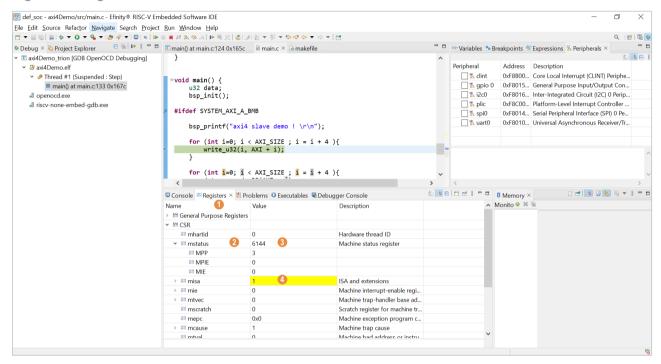

| CSR Register View                                       |      |

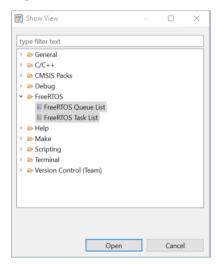

| FreeRTOS View                                           |      |

| QEMU Emulator                                           | 49   |

| Chapter 8: Concurrent Debugging                         |      |

| Enable Concurrent Debugging                             |      |

| Disable Concurrent Debugging                            |      |

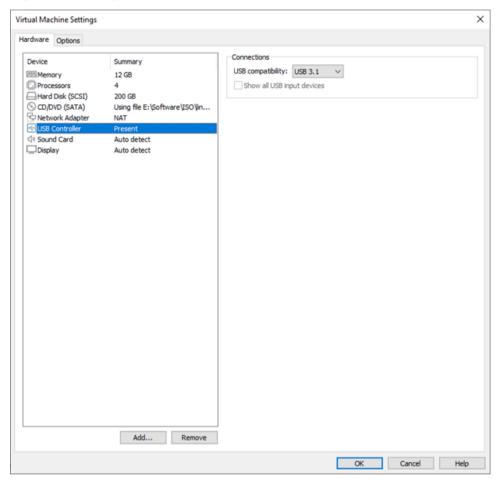

| Concurrent Debugging with Multiple Devices              |      |

| Semihosting with Concurrent Debugging                   | 59   |

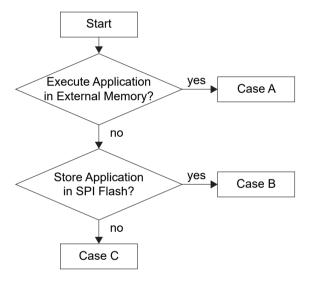

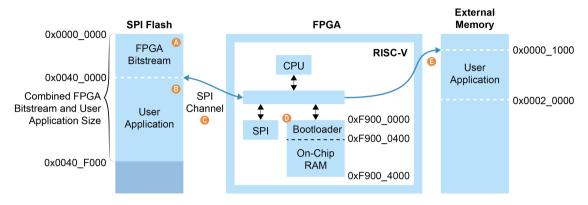

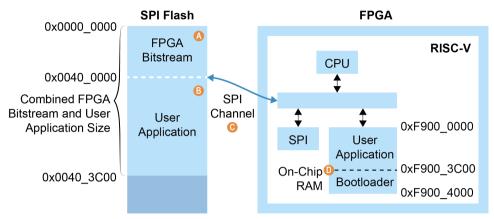

| Chapter 9: Boot Sequence                                |      |

| Boot Sequence: Case A                                   |      |

| Boot Sequence: Case B                                   |      |

| Boot Sequence: Case C                                   |      |

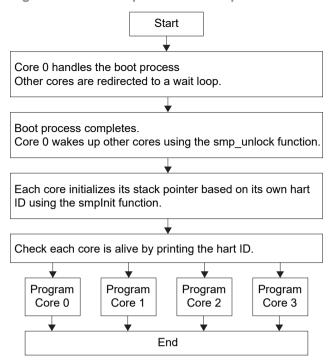

| Booting Multiple Cores                                  |      |

| Chapter 10: Create Your Own RTL Design                  |      |

| Target another FPGA                                     |      |

| Target Your Own Board                                   | 67   |

| Chapter 11: Create Your Own Software                    | 69   |

| Root from a Elach Dovice                                                   |                                                        |

|----------------------------------------------------------------------------|--------------------------------------------------------|

| Boot nom a Flash Device                                                    | 69                                                     |

| Boot from the OpenOCD Debu                                                 | gger70                                                 |

|                                                                            | finity Programmer)70                                   |

|                                                                            | 7 <sup>*</sup>                                         |

|                                                                            | 72                                                     |

|                                                                            | 75                                                     |

|                                                                            | 77                                                     |

|                                                                            |                                                        |

|                                                                            |                                                        |

|                                                                            |                                                        |

|                                                                            |                                                        |

|                                                                            |                                                        |

|                                                                            | 80                                                     |

|                                                                            | 82                                                     |

|                                                                            | 86                                                     |

|                                                                            | 86                                                     |

|                                                                            | 86                                                     |

| inlineAsmDemo                                                              | 87                                                     |

| lwipIperfServer                                                            | 88                                                     |

|                                                                            | 89                                                     |

|                                                                            | 90                                                     |

|                                                                            | 90                                                     |

|                                                                            | 9                                                      |

|                                                                            | ı9 <sup>°</sup>                                        |

|                                                                            | 92                                                     |

|                                                                            | 93                                                     |

|                                                                            | 92                                                     |

|                                                                            |                                                        |

|                                                                            | 99                                                     |

|                                                                            | 99                                                     |

|                                                                            |                                                        |

|                                                                            | 97                                                     |

|                                                                            | 97                                                     |

| userTimerDemo                                                              | 98                                                     |

| Chapter 12: Third party Debugger                                           | 9                                                      |

|                                                                            |                                                        |

| Snapter 12: Third-party Debugger                                           |                                                        |

|                                                                            |                                                        |

| Chapter 13: Hardware and Software Migra                                    | tion from Sapphire SoC to Sapphire High-Performance    |

| Chapter 13: Hardware and Software Migrate SoC                              | tion from Sapphire SoC to Sapphire High-Performance    |

| Chapter 13: Hardware and Software Migrate SoCIntroduction                  | tion from Sapphire SoC to Sapphire High-Performance100 |

| Chapter 13: Hardware and Software Migrate SoC IntroductionHardware         | tion from Sapphire SoC to Sapphire High-Performance100 |

| Chapter 13: Hardware and Software Migrate SoCIntroductionHardware          | tion from Sapphire SoC to Sapphire High-Performance100 |

| Chapter 13: Hardware and Software Migrate SoC IntroductionHardwareSoftware | tion from Sapphire SoC to Sapphire High-Performance100 |

| Chapter 13: Hardware and Software Migrate SoC                              | tion from Sapphire SoC to Sapphire High-Performance    |

| Chapter 13: Hardware and Software Migrat SoC                               | tion from Sapphire SoC to Sapphire High-Performance    |

| Chapter 13: Hardware and Software Migrate SoC                              | tion from Sapphire SoC to Sapphire High-Performance    |

| Chapter 13: Hardware and Software Migrat SoC                               | tion from Sapphire SoC to Sapphire High-Performance    |

| Chapter 13: Hardware and Software Migrat SoC                               | tion from Sapphire SoC to Sapphire High-Performance    |

| Chapter 13: Hardware and Software Migrat SoC                               | tion from Sapphire SoC to Sapphire High-Performance    |

| Chapter 13: Hardware and Software Migrat SoC                               | tion from Sapphire SoC to Sapphire High-Performance    |

| Chapter 13: Hardware and Software Migrat SoC                               | tion from Sapphire SoC to Sapphire High-Performance    |

| Chapter 13: Hardware and Software Migrat SoC                               | tion from Sapphire SoC to Sapphire High-Performance    |

| Chapter 13: Hardware and Software Migrat SoC                               | tion from Sapphire SoC to Sapphire High-Performance    |

| Chapter 13: Hardware and Software Migrat SoC                               | tion from Sapphire SoC to Sapphire High-Performance    |

| Chapter 13: Hardware and Software Migrat SoC                               | tion from Sapphire SoC to Sapphire High-Performance    |

| Chapter 13: Hardware and Software Migrat SoC                               | tion from Sapphire SoC to Sapphire High-Performance    |

| Chapter 13: Hardware and Software Migrat SoC                               | tion from Sapphire SoC to Sapphire High-Performance    |

| Chapter 13: Hardware and Software Migrat SoC                               | tion from Sapphire SoC to Sapphire High-Performance    |

| Chapter 13: Hardware and Software Migrat SoC                               | tion from Sapphire SoC to Sapphire High-Performance    |

| Chapter 13: Hardware and Software Migrat SoC                               | tion from Sapphire SoC to Sapphire High-Performance    |

| Chapter 13: Hardware and Software Migrat SoC                               | tion from Sapphire SoC to Sapphire High-Performance    |

| Chapter 13: Hardware and Software Migrat SoC                               | tion from Sapphire SoC to Sapphire High-Performance    |

| OpenOCD Error: timed out while waiting for target halted  | 117 |

|-----------------------------------------------------------|-----|

| Efinity Debugger Crashes when using OpenOCD               |     |

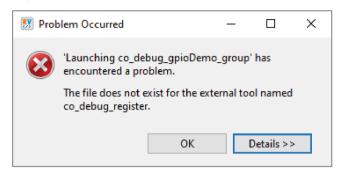

| Non-existing file for the co_debug_register external tool |     |

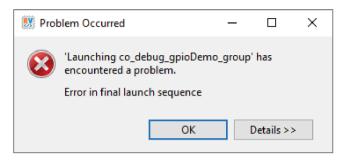

| Error in Final Launch Sequence                            |     |

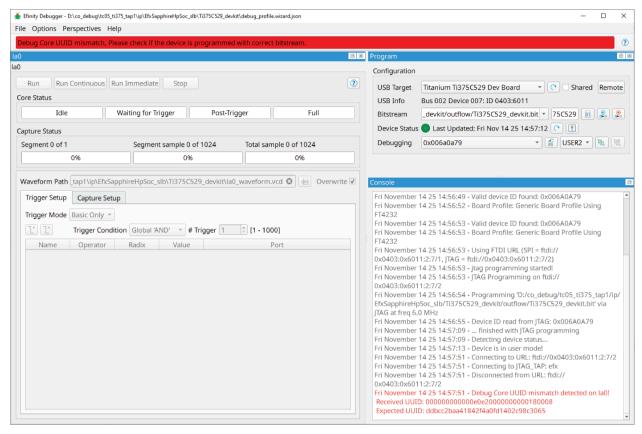

| Debug Core UUID Mismatch                                  |     |

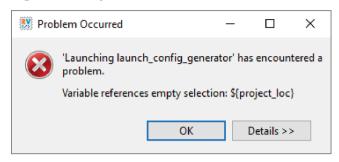

| Variable references empty selection: \${project_loc}      |     |

| Chapter 19: API Reference                                 | 123 |

| Control and Status Registers                              | 124 |

| GPIO API Calls                                            | 126 |

| I <sup>2</sup> C API Calls                                | 129 |

| I/O API Calls                                             | 139 |

| Core Local Interrupt Timer API Calls                      | 141 |

| User Timer API Calls                                      | 142 |

| PLIC API Calls                                            | 143 |

| SPI API Calls                                             | 145 |

| SPI Flash Memory API Calls                                | 147 |

| UART API Calls                                            | 151 |

| RISC-V API Calls                                          | 153 |

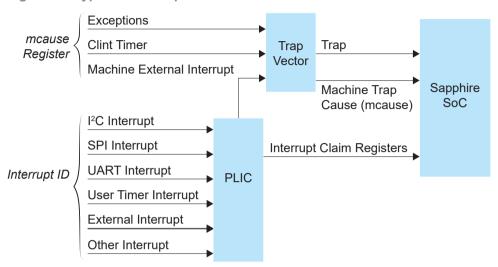

| Handling Interrupts                                       | 154 |

| Chapter 20: Inline Assembly                               | 157 |

| Introduction                                              |     |

| Inline Assembly Syntax                                    | 158 |

| Operands                                                  |     |

| RISC-V Registers                                          | 163 |

| Revision History                                          |     |

|                                                           |     |

## Introduction

Elitestek provides a hardened RISC-V SoC, called Sapphire High-Performance SoC, that you can implement in tandem with the soft logic block on the TJ-Series TJ375 FPGA.

This hardened SoC features a 32-bit quad-core RISC-V processor based on the RISCV32I ISA<sup>(1)</sup> with M, A, C, F, and D extensions. It operates with six pipeline stages: fetch, injector, decode, execute, memory, and writeback.

Each CPU core includes a dedicated FPU and supports custom instructions. The processor follows the standard RISC-V debug specification and providing 8 hardware breakpoints. Additionally, it supports machine and supervisor privileged modes, along with Linux MMU SV32 page-based virtual memory.

This user guide describes how to:

- Build RTL designs using the Sapphire High-Performance RISC-V SoC using an example design targeting TJ-Series TJ375 N529 Development Board, and how to extend the example for your own application.

- Set up the software development environment using an example project, create your own software based on example projects, and use the API.

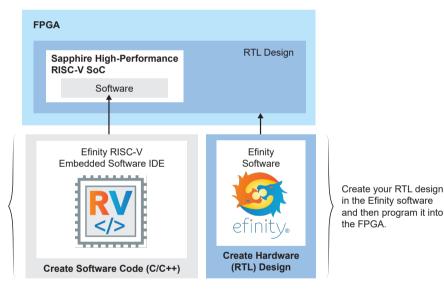

Figure 1: Designing Hardware and Software for the Sapphire High-Performance RISC-V SoC

Write your C/C++ code using our Efinity RISC-V Embedded software IDE, then copy it to the flash memory.

Learn more: Refer to the Sapphire High-Performance RISC-V SoC Data Sheet for detailed specifications on the SoC.

<sup>(1)</sup> ISA: Instruction Set Architecture

# Efinity® RISC-V Embedded Software IDE

The Efinity® RISC-V Embedded Software IDE is an Eclipse-based Integrated Development Environment (IDE) powered by Ashling's *RiscFree*™ IDE for Sapphire High-Performance SoC. It provides a complete and seamless environment for RISC-V C and C++ software development.

#### Features include:

- Eclipse based IDE with full source project creation, edit, build, and debug

- QEMU emulator support for 32-bit RISC-V cores with out-of-box example design

- High-level Peripheral Register viewer

- Control and Status Register (CSR) viewer

- Integrated new project creation process with Board Support Package (BSP) generated in the Efinity software

- Integrated example program import process with Board Support Package (BSP) generated in the Efinity software

- Integrated serial terminal for viewing UART data

- FreeRTOS task and queue list debug view

- Debug support for all OpenOCD compliant probes

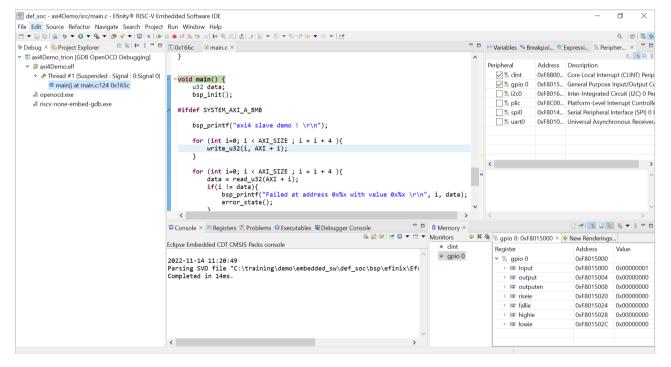

Figure 2: Efinity RISC-V Embedded Software IDE

# Required Software

To write software for the Sapphire High-Performance SoC, you need the following tools. The Efinity RISC-V Embedded Software IDE installer for Windows and Linux operating systems are available in the **Elitestek website**.

## Efinity® Software

Elitestek® development environment for creating RTL designs targeting Trion®, TJ-Series, or TP-Series FPGAs. The software provides a complete RTL-to-bitstream flow, simple, easy to use GUI interface, and command-line scripting support.

## Efinity RISC-V Embedded Software IDE

The Efinity RISC-V Embedded Software IDE is an Eclipse-based Integrated Development Environment (IDE) powered by Ashling's *RiscFree*™ IDE for Sapphire High-Performance SoC and provides a complete provides a complete, seamless environment for RISC-V C and C++ software development. The RISC-V IDE includes the following packages:

Disk space required: 2.4 GB (Windows), 2.5 GB (Linux)

xPack GNU RISC-V Embedded GCC—Open-source, prebuilt toolchain from the xPack Project.

Version: 8.3.0-2.3

Disk space required: 1.53 GB (Windows), 1.5 GB (Linux)

**OpenOCD Debugger**—The open-source Open On-Chip Debugger (OpenOCD) software includes configuration files for many debug adapters, chips, and boards. Many versions of OpenOCD are available. The Elitestek RISC-V flow requires a custom version of OpenOCD that includes the VexRiscv 32-bit RISC-V processor.

Version: 0.11.0 (20240413)

Disk space required: 17.4 MB (Windows), 16.3 MB (Linux)

**Note:** Elitestek recommends you use the latest version of Efinity RISC-V Embedded Software IDE to ensure compatibility with Efinity software.

## Required Hardware

- TJ-Series TJ375 N529 Development Board

- 12 V power cable

- USB C-cable

- Computer or laptop

- FAT32 formatted SD card

- Cat 5e Ethernet cable and above

# Comparison with Sapphire SoC

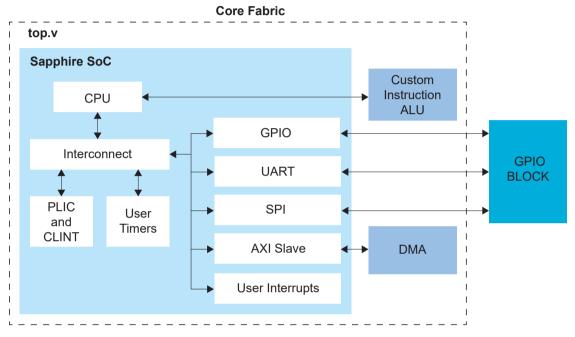

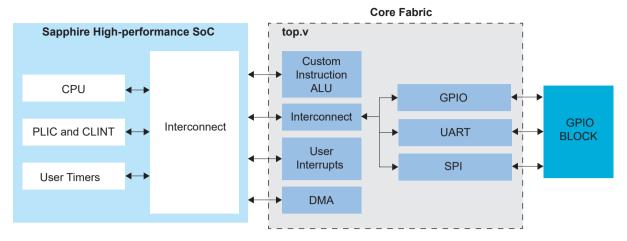

While the Sapphire High-Performance SoC architecture shares similarities with the Sapphire SoC, there are notable differences to consider:

## Sapphire SoC

- · User peripherals connected via internal bus.

- No data coherency between CPU and DMA via AXI Slave port.

- · Absence of a branch predictor.

- Uses a shared FPU configuration for multi-core setups.

- Supports up to 4 configurable hardware breakpoints.

### Sapphire High-Performance SoC

- User peripherals are segmented into separate modules, with EfxSapphireHpSoc\_slb connected via AXI master interface. Note that the base address and AXI master interface are dedicated to this module. If additional modules require AXI mastere access, an AXI interconnect IP can facilitate connections to both EfxSapphireHpSoc slb and your module.

- Ensure data coherency between CPU and DMA via AXI Slave port, potentially eliminating the need for data cache flushing.

- Features an integrated static branch predictor.

- Dedicated FPU per core.

- Supports 8 hardware breakpoints for debug module.

## **Performance**

The following table shows the overall performance of Sapphire High-Performance SoC.

Table 1: Key Performance of Sapphire High-Performance SoC

| Test/Benchmark      | Result             |                    |  |

|---------------------|--------------------|--------------------|--|

| Dhrystone Baremetal | 1.2375 DMIPS/MHz   | 1.2375 DMIPS/MHz   |  |

| Coremark Baremetal  | 2.345 Coremark/MHz | 2.345 Coremark/MHz |  |

| Coremark Linux      | 2.222 Coremark/MHz |                    |  |

| Coremark Pro Linux  | Multi Core 581.67  |                    |  |

|                     | Single Core 167.46 |                    |  |

|                     | Scaling 3.47       |                    |  |

## Configuration:

System clock: 1.0 GHzMemory clock: 250 MHz

• DDR clock: 800 MHz (3.2 Gbps) @ x32 data lanes

# Install Software and SoC

#### Contents:

- Install the Efinity Software

- Install the Efinity RISC-V Embedded Software IDE

# Install the Efinity Software

If you have not already done so, download the Efinity software from the Support Center and install it. For installation instructions, refer to the **Efinity Software Installation User Guide**.

Warning: Do not use spaces or non-English characters in the Efinity path.

## Install the Efinity RISC-V Embedded Software IDE

Download the installer file in **Efinity RISC-V Embedded Software IDE <version>** from the Support Center.

To install the Efinity RISC-V Embedded Software IDE:

#### **Windows**

- 1. Execute the installer file efinity-riscv-ide-<version>-windows-x64.exe to launch the installer.

- 2. Follow the steps in the setup process.

- Install Efinity RISC-V IDE in a preferred directory or use the default directory c:\Efinity\efinity-riscv-ide-<version>\. Example, c:\Efinity\efinity-riscv-ide-2022.2.3\.

#### Linux

Execute the installer file efinity-riscv-ide-<version>-linux-x64.run or run the installer using ./<installer run file>. Run the executable script with command:

chmod +x <installer run file>

- 2. Select either to install the RISC-V IDE for the current user or multiple users.

- 3. Follow the steps in the setup wizard.

- 4. Install Efinity RISC-V IDE in a preferred directory or use the default directory /home/user/efinity/efinity-riscv-ide-version>. Example, /home/user/efinity/efinity-riscv-ide-2022.2.3/.

#### Note:

- Elitestek provides FREE licences for the Efinity software. Alternatively, when you buy a development kit, you also

get a software license and one year of upgrades. After the first year, you can request a free maintenance renewal.

The Efinity software is available for download from the Elitestek website. To get your free license, create an account,

login, and then go to the Efinity page to request your license.

- Elitestek recommends you use the latest version of Efinity RISC-V Embedded Software IDE to ensure compatibility with Efinity software.

# **IP Manager**

#### Contents:

- Customizing the Sapphire High-Performance SoC

- Modify the Bootloader

The Efinity® IP Manager is an interactive wizard that helps you customize and generate Elitestek® IP cores. The IP Manager performs validation checks on the parameters you set to ensure that your selections are valid. When you generate the IP core, you can optionally generate an example design targeting an Elitestek development board and/or a testbench. This wizard is helpful in situations in which you use several IP cores, multiple instances of an IP core with different parameters, or the same IP core for different projects.

The IP Manager consists of:

- IP Catalog—Provides a catalog of IP cores you can select. Open the IP Catalog using the toolbar button or using Tools > Open IP Catalog.

- *IP Configuration*—Wizard to customize IP core parameters, select IP core deliverables, review the IP core settings, and generate the custom variation.

- IP Editor—Helps you manage IP, add IP, and import IP into your project.

## Generating Sapphire High-Performance SoC with the IP Manager

Hardened SoC - Hardened RISC-V Block (HRB) Core Fabric - Soft Logic Block (SLB) CPU 3 CPU 2 CPU 1 CPU 0 VexRiscy (IMACFD) Custom Instruction PHS Soft JTAG FPU DMA Accelerato 4-way 16 KB Data Caches 4-way 16 KB Instruction Caches AXI4 Slave Coherency AXI4 Master AXI Interconnect Manager 256 MB \$ Ť Bus AXI Port 0 3.7 GB I PDDR4/4X External I<sup>2</sup>C, SPI, UART, GPIO System Bus APB Memory Controller AXI Interface From User Interrupts (CPU) 16 KB On-Chip User User PLIC Timer 2 RAM Timer 1

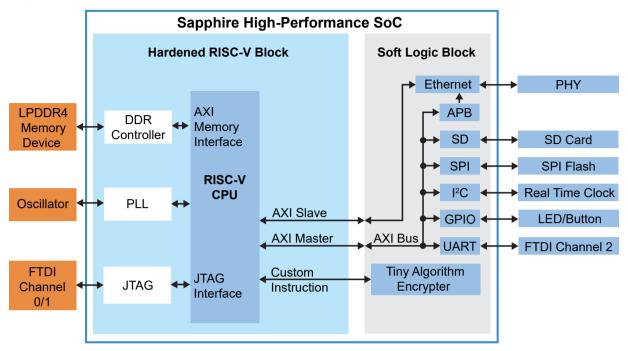

Figure 3: Overall Block Diagram of Sapphire High-Performance SoC

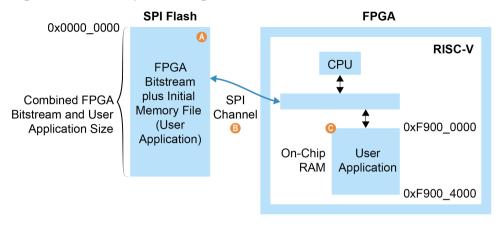

The Sapphire High-Performance SoC consists of two (2) parts, the hardened RISC-V block (HRB) and the soft logic block (SLB). The HRB includes a quad-core CPU, caches, memory management, debug module, on-chip RAM, and data traffic management. In contrast, the SLB is formed by soft logic to exercise I/O control, custom ALU, and DMA. In relation, the IP Manager helps to configure the hardened blocks and instantiate the common-use controllers like SPI, I2C, GPIO, and UART. Additionally, the IP manager assists by configuring the required blocks like PLLs and LPDDR4 controllers.

The following steps explain how to customize an IP core with the IP Configuration wizard.

- 1. Open the IP Catalog.

- 2. Choose an IP core and click **Next**. The **IP Configuration** wizard opens.

- 3. Enter the module name in the Module Name box.

**Note:** The Sapphire High-Performance SoC soft logic block module name is fixed to **EfxSapphireHpSoc slb**.

- **4.** Customize the IP core using the options shown in the wizard. For detailed information on the options, refer to the IP core's user guide or on-line help.

- **5.** (Optional) In the **Deliverables** tab, specify whether to generate an IP core example design targeting an Elitestek® development board and/or testbench. For SoCs, you can also optionally generate embedded software example code. These options are turned on by default.

- 6. (Optional) In the Summary tab, review your selections.

- 7. Click **Generate** to generate the IP core and other selected deliverables.

- 8. In the **Review configuration generation** dialog box, click **Generate**. The Console in the **Summary** tab shows the generation status.

**Note:** You can disable the **Review configuration generation** dialog box by turning off the **Show Confirmation Box** option in the wizard.

**9.** When generation finishes, the wizard displays the **Generation Success** dialog box. Click **OK** to close the wizard.

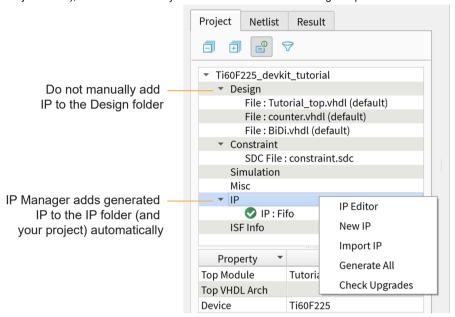

The wizard adds the IP to your project and displays it under IP in the Project pane.

#### Generated RTL Files

The IP Manager generates these files and directories:

- <module name> define.vh—Contains the customized parameters.

- <module name>\_tmpl.v—Verilog HDL instantiation template.

- <module name> tmpl.vhd—VHDL instantiation template.

- <module name>.v—IP source code.

- settings.json—Configuration file.

- <kit name>\_devkit—Has generated RTL, example design, and Efinity® project targeting

a specific development board.

Note: Refer to the IP Manager chapter of the Efinity Software User Guide for more information about the Efinity IP Manager.

## Generated Software Code

If you choose to output embedded software, the IP Manager saves it into the croject>I

embedded\_sw/efx\_hard\_soc

directory.

- bsp—Board specific package.

- **software**—Software examples, includes FreeRTOS and baremetal demos.

## Instantiating the Hardened RISC-V SoC

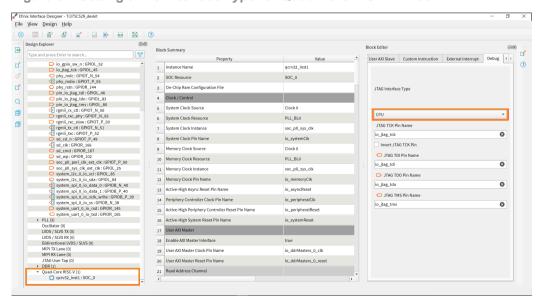

The IP manager helps to instantiate the hardened RISC-V block from the Efinity's Interface Designer which includes:

- Assigning top-level signal name to the block.

- Instantiating dedicated PLL to the hardened RISC-V block.

- Instantiating the required GPIO block.

- · Assigning pre-defined pins to GPIO block.

## Instantiating the SoC Soft Logic Block

The IP Manager creates these template files in the /ip/<module name> directory:

- <module name>.v\_tmpl.v is the Verilog HDL module.

- <module name>.v\_tmpl.vhd is the VHDL component declaration and instantiation template.

- EfxSapphireHpSoc\_wrapper.v is the wrapper file for soft logic block design.

To use the IP, copy and paste the code from the template file into your design and update the signal names to instantiate the IP.

**Important:** When you generate the IP, the software automatically adds the module file (<module name>.v) to your project and lists it in the IP folder in the Project pane. Do not add the <module name>.v file manually (for example, by adding it using the Project Editor); otherwise the Efinity® software will issue errors during compilation.

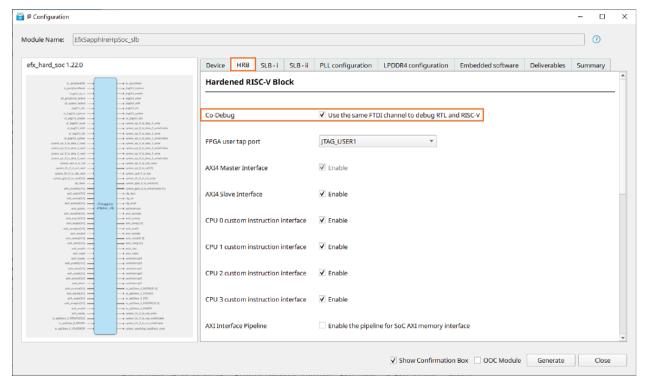

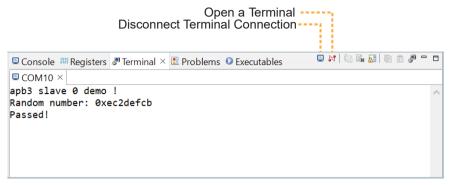

# Customizing the Sapphire High-Performance SoC

You customize the Sapphire High-Performance SoC using the IP Configuration wizard. The parameters are arranged on tabs so you can click through them more easily.

Table 2: Sapphire High-Performance Hardened RISC-V Device Selection Tab

| Parameter | Options              | Description                                                                                                                                                                                     |  |

|-----------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Family    | TJ-Series, TP-Series | Device Family Selection.                                                                                                                                                                        |  |

|           |                      | Note: If you are updating your TP-Series project with the SLB software version that is lower than v1.19, you are recommended to regenerate the SLB again when the software is updated to v1.19. |  |

| Package   | 484, 529, 900, 1156  | Package selection.                                                                                                                                                                              |  |

|           |                      | Current supported package for TP-Series: 484, 529                                                                                                                                               |  |

|           |                      | Current supported package for TJ-Series: All pakcage                                                                                                                                            |  |

Table 3: Sapphire High-Performance Hardened RISC-V Block Tab Parameters

| Parameter                          | Options                                                 | Description                                                                                                                                                                                                                                                     |  |

|------------------------------------|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| JTAG Debug Interface               | FPGA User Tap,<br>JTAG with GPIO                        | Choose whether to include a soft debug TAP for debugging.  FPGA User Tap: The SoC uses the JTAG User Tap interface block to communicate with the OpenOCD debugger.  JTAG with GPIO: The SoC has a soft JTAG interface to communicate with the OpenOCD debugger. |  |

| FPGA User Tap Port                 | JTAG_USER1,<br>JTAG_USER2,<br>JTAG_USER3,<br>JTAG_USER4 | Choose the tap port to target with the OpenOCD debugger. This option only applies when using the JTAG user tap interface block to communicate with the OpenOCD debugger.                                                                                        |  |

| AXI4 Slave Interface               | On, off                                                 | On: Instantiate the interface.  Off: Do not use the interface.  Note: The Efinity software v2025.2 and higher uses AXI slave instead of AXI master as the interface name.                                                                                       |  |

| AXI4 Master Interface              | On, off                                                 | On: Instantiate the interface. Off: Do not use the interface. This interface is forcibly enabled for peripheral interfacing.  Note: The Efinity software v2025.2 and higher uses AXI master instead of AXI slave as the interface name.                         |  |

| CPU n Custom Instruction Interface | On, off                                                 | On: Instantiate the interface.  Off: Do not use the interface.                                                                                                                                                                                                  |  |

| AXI Interface Pipeline             | On, off                                                 | Enable the pipeline for Soc AXI Memory Interface.                                                                                                                                                                                                               |  |

| AXI Write Buffer                   | On, off                                                 | Bypass the AXI write buffer.                                                                                                                                                                                                                                    |  |

| User Interrupt Ports               | 0 - 24                                                  | O: Do not use interrupt port.  1 - 24: The number of interrupt port that turns on.                                                                                                                                                                              |  |

| OCR Application                    | On, off                                                 | On: Overwrite the default SPI flash bootloader with the user application.  Off: Initialize SoC without user application.                                                                                                                                        |  |

| User Application                   | _                                                       | Enter the path to your target user application. The file must be in . hex format.                                                                                                                                                                               |  |

13

Table 4: Sapphire High-Performance Soft Logic Block Tab Parameters

| Parameter                       | Options                             | Description                                                                                                                                |  |

|---------------------------------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--|

| Peripheral Interconnect         | On, off                             | On: Instantiate an interconnect with peripherals attached to it.                                                                           |  |

|                                 |                                     | Off: Do not use the interconnect generated by the IP Manager.                                                                              |  |

| Pin Resource<br>Assignment      | On, off                             | On: Update project peri.xml to instantiate required GPIO blocks for enabled peripherals. Off: Do not update project peri.xml               |  |

| Pin Assignment                  | On, off                             | On: Update project peri.xml to assign pre-defined pins to GPIO blocks.                                                                     |  |

|                                 |                                     | Off: Do not update project peri.xml.                                                                                                       |  |

| Required SoC Interrupt<br>Ports | -                                   | Show required interrupts for enabled peripherals.                                                                                          |  |

| Uart Controller n               | On, off                             | On: Instantiate the controller.                                                                                                            |  |

|                                 |                                     | Off: Do not use the controller.                                                                                                            |  |

| SPI Controller n                | On, off                             | On: Instantiate the controller.                                                                                                            |  |

|                                 |                                     | Off: Do not use the controller.                                                                                                            |  |

| I2C Controller n                | On, off                             | On: Instantiate the controller.                                                                                                            |  |

|                                 |                                     | Off: Do not use the controller.                                                                                                            |  |

| GPIO Controller n               | On, off                             | On: Instantiate the controller.                                                                                                            |  |

|                                 |                                     | Off: Do not use the controller.                                                                                                            |  |

| Specify GPIO n pin width        | 4, 8, 16, 24, 32                    | Specify the number of pins to be enabled for the GPIO controller.                                                                          |  |

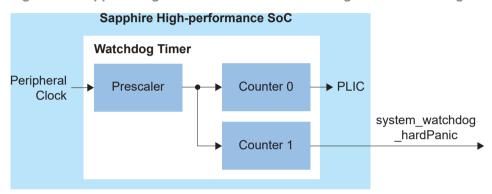

| Watchdog Timer                  | On, off                             | On: Instantiate the watchdog timer.                                                                                                        |  |

|                                 |                                     | Off: Do not use the watchdog timer.                                                                                                        |  |

| APB3 interface n                | On, off                             | On: Instantiate the interface.                                                                                                             |  |

|                                 |                                     | Off: Do not use the interface.                                                                                                             |  |

| Specify APB3 n size             | 4 KB, 16 KB, 64 KB,<br>256 KB, 1 MB | Specify the size of the APB interface.                                                                                                     |  |

| SD Host Controller              | On, off                             | Instantiate SD host controller ip and integrate into soc wrapper file the interface. To be supported in the upcoming 2024.1 patch release. |  |

| Triple-speed Ethernet MAC       | On, off                             | Instantiate ethernet controller ip and integrate into soc wrapper file. To be supported in the upcoming 2024.1 patch release.              |  |

**Table 5: Sapphire High-Performance PLL Configuration Tab Parameters**

| Parameter                    | Options                                    | Description                                                                                                                                      |

|------------------------------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| System Clock PLL             |                                            |                                                                                                                                                  |

| Pin Assignment               | On, off                                    | On: Update project peri.xml to include this PLL.  Off: Do not update project peri.xml                                                            |

| Instance Name                | Fixed string                               | The PLL instance name will be configured later in the Interface Designer.                                                                        |

| PLL Resource                 | PLL_BL0,<br>PLL_BL1,<br>PLL_BL2            | Choose which PLL resource you want to utilize in Interface Designer.                                                                             |

| PLL External Clock<br>Source | Clock 0,<br>Clock 1                        | Specify which external clock source as reference clock to PLL.                                                                                   |

| Reference Clock<br>Frequency | Input value in MHz                         | Specify reference clock frequency.                                                                                                               |

| System Clock Frequency       | 250 - 1000 MHz                             | Specify the system clock frequency that drives most of the logic of the hardened RISC-V block including CPU, FPU, MMU, caches, on-chip RAM, etc. |

| Memory Clock<br>Frequency    | 25 - 250 MHz                               | Specify the memory clock frequency that drives the AXI traffic to external memory.                                                               |

| DDR Clock Frequency          | 200 - 900 MHz                              | Specify the DDR clock frequency that is input to the DDR controller.                                                                             |

| Peripheral Clock PLL         |                                            |                                                                                                                                                  |

| Pin Assignment               | On, off                                    | On: Update project peri.xml to include this PLL. Off: Do not update project peri.xml                                                             |

| Instance Name                | Fixed string                               | The PLL instance name that will be configured later in the Interface Designer.                                                                   |

| PLL Resource                 | PLL_BLn,<br>PLL_BRn<br>PLL_TLn<br>PLL_TRn, | Choose which PLL resource you want to utilize in Interface Designer. The PLL resource cannot be the same as system clock PLL.                    |

| PLL External Clock<br>Source | Clock 0<br>Clock 1                         | Specify which external clock source as reference clock to PLL.                                                                                   |

| Reference Clock<br>Frequency | Input value in MHz                         | Specify reference clock frequency.                                                                                                               |

| Peripheral Clock             | 25 - 250 MHz                               | Specify peripheral clock frequency that drives soft logic block logic.                                                                           |

| AXI4 Slave Clock             | 25 - 250 MHz                               | Specify AXI4 slave clock.                                                                                                                        |

| Custom Instruction Clock     | 25 - 250 MHz                               | Specify custom instruction clock frequency.                                                                                                      |

**Table 6: Sapphire High-Performance LPDDR4 Configuration Tab Parameters**

| Parameter            | Options                                       | Description                                                                                |

|----------------------|-----------------------------------------------|--------------------------------------------------------------------------------------------|

| Device Setting       | •                                             |                                                                                            |

| LPDDR4 Controller    | On, off                                       | On: Update project peri.xml to include this configuration.                                 |

| Assignment           |                                               | Off: Do not update project peri.xml                                                        |

| Instance Name        | Fixed string                                  | The DDR instance name will be configured later in the Interface Designer.                  |

| Memory Data Width    | 16, 32                                        | The DDR device data width.                                                                 |

| Memory Density       | 2 GB, 3 GB, 4 GB, 6 GB,<br>8 GB, 12 GB, 16 GB | The DDR device memory density.                                                             |

| Memory Type          | LPDDR4, LPDDR4x                               | The DDR device memory type.                                                                |

|                      |                                               | TP-Series device only supports LPDDR4 memory type with maximum clock frequency of 600 MHz. |

| Memory Physical Rank | 1, 2                                          | The DDR device memory physical rank.                                                       |

**Table 7: Sapphire High-Performance Embedded Software Configuration**

| Parameter             | Options                                                                                                         | Description                                                                |

|-----------------------|-----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| FTDI Type             | Single Channel<br>Dual Channel<br>Quad Channel                                                                  | Specify the number of channels available for the FTDI device use.          |

| FTDI Debug Channel    | Channel 0,Channel 1,<br>Channel 2,Channel 3                                                                     | Specify which channel the JTAG connected.                                  |

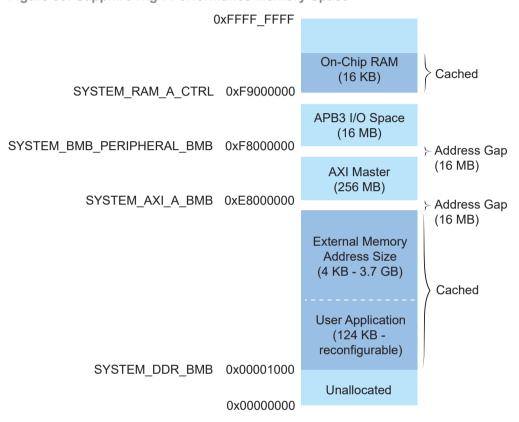

| Application Size      | 124 KB, 252 KB, 324<br>KB, 508 KB, 1 MB, 2<br>MB, 4 MB, 8 MB, 16<br>MB, 32 MB, 64 MB, 128<br>MB, 256 MB, Custom | Specify the size allocated for application in linker scripts.              |

| Application Size (KB) | -                                                                                                               | Specify the custom size allocated for application in linker scripts.       |

| Stack Size            | 1 KB, 2 KB, 4 KB, 8 KB, 16<br>KB, 32 KB, 64 KB, 128 KB,<br>256 KB, 512 KB, Custom                               | Specify the size allocated for application stack in linker scripts.        |

| Stack Size (KB)       | -                                                                                                               | Specify the custom size allocated for application stack in linker scripts. |

# Modify the Bootloader

When you generate the Sapphire High-Performance SoC, the IP Manager does not include any pre-built firmware to target the on-chip RAM size you selected. You can compile SPI flash bootloader software codes in the **embedded\_sw/efx\_hard\_soc/software/standalone/bootloader**

Learn more: You need to install Efinity RISC-V Embedded Software IDE to compile the bootloader or other software.

**Note:** By default, the bootloader uses only a single data line SPI. To use dual or quad data line SPI, refer to **Modify the Bootloader Software to Enable Multi-Data Lines** on page 18.

## Modify the Bootloader Software to Extend the External Memory Size

First you need to modify the bootloader code:

- Open the bootloaderConfig.h file in the embedded\_sw/efxh\_hard\_soc/software/ standalone/bootloader directory.

- Change the #define USER\_SOFTWARE\_SIZE parameter for the new on-chip RAM size and save.

- **3.** In Efinity RISC-V Embedded Software IDE, import **standalone/bootloader** project. Build the project to generate new **bootloader.hex** file.

Second, you update and re-generate the SoC in the IP Manager to point to your new **bootloader.hex** and change the application region size. The default maximum size is 324 KB.

- 1. In the Sapphire High-Performance IP wizard, go to the **HRB** tab.

- 2. Turn on the OCR Application option.

- Click the Browse button to select the new bootloader.hex you created in the previous set of steps.

- 4. Generate the SoC.

## Modify the Bootloader Software to Enable Multi-Data Lines

Before utilizing the multi-data lines SPI in your bootloader, ensure your board's flash device supports Dual or Quad I/O modes.

In the Efinity RISC-V Embedded Software IDE example design, data ports 0 and 1 are exclusively connected. If you intend to use the Quad SPI for data transfer, you must establish connections for data ports 2 and 3. The following table shows the number of connected data lines interfacing with the respective FPGAs and flash devices.

Table 8: Multi Data Lines Interface with FPGAs and Flash Devices

| Development Kit | Flash device     | Number of Data Lines Connected |

|-----------------|------------------|--------------------------------|

| TJ375N529       | IS25WP512M-JLLA3 | 4                              |

| TJ375N1156X     | GD25LB512MEYIGR  | 4                              |

In the bootloaderConfig.h file, you can define your preferred SPI lane configuration by selecting from the following data line modes:

- SINGLE SPI: Single data line • DUAL SPI: Dual data line QUAD SPI: Quad data line

- #define SINGLE SPI 1 //define DUAL SPI for dual data SPI or QUAD SPI for quad data SPI void bsp Main() #ifndef SIM spiFlash\_init(SPI, SPI\_CS);

spiFlash\_wake(SPI, SPI\_CS);

spiFlash\_exit4ByteAddr(SPI, SPI\_CS); #ifdef SINGLE SPI spiFlash\_f2m(SPI, SPI\_CS, USER\_SOFTWARE\_FLASH, USER\_SOFTWARE\_MEMORY, USER SOFTWARE SIZE); #elif DUAL SPI spiflash f2m dual(SPI, SPI CS, USER\_SOFTWARE\_FLASH, USER\_SOFTWARE\_MEMORY, USER\_SOFTWARE\_SIZE); //dual data line half duplex #elif QUAD\_SFI spIrlash f2m quad(SPI, SPI\_CS, USER\_SOFTWARE\_FLASH, USER\_SOFTWARE\_MEMORY, USER\_SOFTWARE\_SIZE); //quad data line full duplex #error "You must either define SINGLE\_SPI to use single data line SPI, DUAL\_SPI to use

dual data line SPI or QUAD\_SPI to use quad data line SPI." #endif #endif void (\*userMain)() = (void (\*)())USER SOFTWARE MEMORY; #ifdef SMP smp\_unlock(userMain); #endif userMain();

Note: If the flash device is GD25 (from TJ375N1156Xdevelopment kit), add CFLAGS+=-DGD25 FLASH before the LDSCRIPT? =\${BSP\_PATH}linker/bootloader.Id into the bootloader application's makefile. Defining the GD25 includes the required commands specific to the GD25 flash device.

# Recommended Design Practice

## Instantiate the Sapphire High-Performance SoC and Soft Logic Block Using the **IP Manager**

Before you integrate your design with the Sapphire High-Performance SoC, you need to generate the RISC-V block and soft logic block together, with the PLL and GPIO resource allocation, and pin assignment. This first step allows you to bring up a working design and having a reference for your next-step debugging. You are free to change the configuration, pins, or block resources later with the interface designer as you can bypass the interface designer configuration update shall you require to re-generate the soft logic block design files with the custom interface designer configuration.

## **PLL Utilization**

The Sapphire High-Performance SoC requires at least 3 crucial clocks:

- System clock—Drives most of the logic within the SoC including CPUs, FPU, MMU, caches, on-chip RAM, etc.

- Memory clock—Drives the AXI path to communicate with the DDR controller.

- DDR controller clock—Input clock for the DDR controller.

Note: Elitestek recommends you use the same PLL to drive the clocks to save the utilization of PLL. Only three PLLs are supported to deliver the clock path to RISC-V block. If you have doubts about the PLL assignment, you may generate the working design with IP Manager.

The following table shows the assignment of the clock.

**Table 9: Clock Assignment**

| PLL Resource        | Output Clock | Functionality |

|---------------------|--------------|---------------|

| PLL_BL0 and PLL_BL2 | Clock 1      | System clock  |

|                     | Clock 2      | Memory clock  |

|                     | Clock 3      | DDR clock     |

| PLL_BL1             | Clock 1      | Memory clock  |

|                     | Clock 2      | System clock  |

|                     | Clock 3      | DDR clock     |

## Soft Logic Block Design Files

The IP Manager generates the design files for soft logic block when you generate the Sapphire High-Performance SoC block. You can see the output files, **EfxSapphireHpSoc\_slb.v** and **EfxSapphireHpSoc\_wrapper.v**.

The **EfxSapphireHpSoc\_slb.v** is the design file that does the following:

- Handles master reset control

- LPDDR4 controller reset and calibration control

- Connects with the selected peripherals in the IP Manager

- Establish a connection between peripherals and user interrupt ports

- Establish a connection between the SoC debug module and the FPGA user tap or GPIO

The **EfxSapphireHpSoc\_wrapper.v** is the example top file for you to refer to and is optional to be included in the project for compilation. You can open and copy the **EfxSapphireHpSoc\_wrapper.v** file to your own top file in directory **ip/EfxSapphireHpSoc\_slb/**. Including the wrapper file in the project compilation list is not recommended. The file can revert to the default design whenever you regenerate the block using IP Manager.

## Handling SoC Interfaces

The Sapphire High-Performance SoC provides the following:

- Custom instruction interface

- AXI master and slave interface

- 24 user interrupt ports to interact with soft logic from FPGA core fabric

You can use a custom instruction interface to deliver the custom ALU for CPU, an AXI slave interface for direct memory access, an AXI master for peripheral communication, and interrupt ports for triggering to access priority routine. However, this can block the SoC from out of reset state if you enable the interfaces but left them unconnected in a design. Hence, you must connect the pins below to a known state even if your design is not ready in the first place.

No further action is required if you disable the interface in the IP Manager.

**Table 10: Clock Assignment**

| Interface          | Pin                              | State |

|--------------------|----------------------------------|-------|

| Custom Instruction | cpuX_customInstruction_cmd_ready | High  |

| AXI Slave          | io_ddrMasters_0_b_ready          | High  |

|                    | io_ddrMasters_0_r_ready          | High  |

# **Example Design**

#### Contents:

- About the Example Design

- Enable the LPDDR4x Memory (TJ375 N529 Board)

- Installing USB Drivers

- Program the Development Board

Before working with software code, Elitestek recommends that you program your board with an RTL design that instantiates the Sapphire High-Performance SoC. When you generate the Sapphire SoC with the IP Manager, you can optionally generate an example Efinity® project and bitstream file to get you started quickly.

## About the Example Design

This example targets TJ-Series development boards:

TJ-Series TJ375 N529 Development Board—The RTL design files are in the TJ375N529 devkit directory.

When you generate the IP core, the IP Manager creates the example design (PLL settings, SDC timing constraints, and I/O assignments).

This example writes to and reads from the development board's memory module using the AXI interface:

For the TJ-Series TJ375 N529 Development Board, the design uses the board's LPDDR4/LPDDR4x DRAM module.

The Sapphire High-Performance SoC is configured for:

- 1000 MHz system clock frequency

- 250 MHz memory clock frequency

- 800 MHz DDR controller clock frequency

- 200 MHz peripheral clock frequency

- 250 MHz AXI slave clock frequency

- 125 MHz custom instruction clock frequency

- Used FPGA user tap 1 for debugging

- Custom instruction for each CPU is enabled

- UART 0 is enabled

- SPI 0 is enabled

- I2C 0 is enabled

- GPIO 0 is enabled

- AXI4 Master is enabled

- AXI Slave 0 is enabled

- 8 User interrupts are enabled

Additional soft IPs like AXI interconnect, SD host controller and ethernet controller are included in the example design.

Figure 4: Example Design Block Diagram

**Table 11: Example Design Implementation**

| FPGA               | Logic +<br>Adders | Flipflops | Multipliers<br>or DSP<br>Blocks | Memory<br>Blocks | f <sub>MAX</sub> (MHz) | Language    | Efinity<br>Version |

|--------------------|-------------------|-----------|---------------------------------|------------------|------------------------|-------------|--------------------|

| TJ375<br>BGA529 C4 | 14,987            | 11,858    | 0                               | 76               | 233                    | Verilog HDL | 2024.1             |

# Enable the LPDDR4x Memory (TJ375 N529 Board)

For the TJ-Series TJ375 N529 Development Board, by default, the SoC design uses LPDDR4x settings to drive the external memory. To enable LPDDR4 setting, change the jumpers on J21 to connect pins 1 and 2 to provide 1.2 V to VDDQ and VDDQ PHY.

Figure 5: Connect Pins 1 and 2 on J21

## **Installing USB Drivers**

To program TJ-Series FPGAs using the Efinity® software and programming cables, you need to install drivers.

Elitestek development board has FT4232H FTDI chip to communicate with the USB port and other interfaces such as SPI, JTAG, or UART. Refer to the Elitestek development kit user guide for details on installing drivers for the development board.

**Note:** If you are using more than one Elitestek development board, you must manage drivers accordingly. Refer to **AN 050: Managing Windows Drivers** for more information.

## **Installing Drivers on Windows**

On Windows, you use software from Zadig to install drivers. Download the Zadig software (version 2.7 or later) from **zadig.akeo.ie**. (You do not need to install it; simply run the downloaded executable.)

Install the driver for the interfaces listed in the following table.

| Board                                  | Interface to Install Driver              |  |

|----------------------------------------|------------------------------------------|--|

| TJ-Series Ti375 C529 Development Board | Install drivers for interfaces (0 and 1) |  |

#### To install the driver:

- 1. Connect the board to your computer with the appropriate cable and power it up.

- 2. Run the Zadig software.

**Note:** To ensure that the USB driver is persistent across user sessions, run the Zadig software as administrator

- 3. Choose Options > List All Devices.

- **4.** Repeat the following steps for each interface. The interface names end with (*Interface N*), where *N* is the channel number.

- Select libusb-win32 in the Driver drop-down list.

- Click Replace Driver.

- Close the Zadig software.

**Note:** This section describes the instruction to install the libusb-win32 driver for each interface separately. If you have previously installed a composite driver or installed using libusbK drivers, you do not need to update or reinstall the driver. They should continue to work correctly.

## **Installing Drivers on Linux**

The following instructions explain how to install a USB driver for Linux operating systems.

- 1. Disconnect your board from your computer.

- 2. In a terminal, use these commands:

```

> sudo <installation directory>/bin/install_usb_driver.sh

> sudo udevadm control --reload-rules

> sudo udevadm trigger

```

**Note:** If your board was connected to your computer before you executed these commands, you need to disconnect it, then re-connect it.

# Program the Development Board

When you generate the Sapphire SoC in the IP Manager, you can optionally generate an example design targeting an Elitestek development board. You need to compile example design to get the bitstream file.

**Table 12: Available Example Designs**

| Board                                  | Location         |

|----------------------------------------|------------------|

| TJ-Series Ti375 C529 Development Board | Ti375C529_devkit |

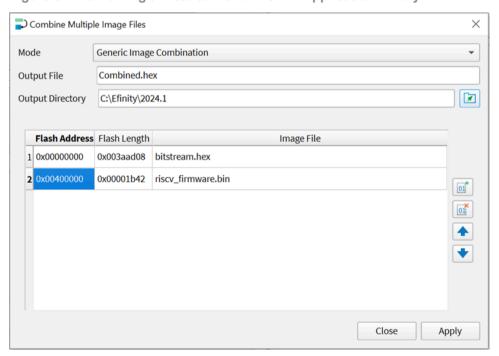

Download the .hex file to the board using these steps:

Connect the board to your computer using a USB cable.

Learn more: Instructions on how to use the Efinity software and board documentation are available in the Elitestek website.

# Launch Efinity RISC-V Embedded Software IDE

#### Contents:

- Launching the Efinity RISC-V Embedded Software IDE

- **IDE Launcher from Efinity**

- **Optimization Settings**

## Launching the Efinity RISC-V Embedded Software IDF

#### **Windows**

Launch the Efinity RISC-V Embedded Software IDE by double-clicking on the Efinity RISC-V IDE shortcut available in the efinity-riscv-ide-<version> folder (example: Efinity-riscvide-2023.2). For easy access, you may transfer the shortcut to the desktop. A new IDE window opens once the IDE is successfully invoked.

You need to select a workspace directory to store the IDE's preferences, configurations and temporary information. Follow these steps:

- Click **Browse** and select your preffered location.

- You may click the **Recent Workspaces** to select a previous workspace.

- Click Launch.

#### Linux

Launch the Efinity RISC-V Embedded Software IDE in a Linux environment by double-clicking the efinity-riscv-ide. Alternatively, you may launch the efinity-riscv-ide in the terminal. A new IDE window opens once the IDE is successfully invoked.

You need to select a workspace directory to store the IDE's preferences, configurations and temporary information. Follow these steps:

- Click **Browse** and select your preffered location.

- You may click the **Recent Workspaces** to select a previous workspace.

- Click Launch.

#### Note:

- You can choose any location for your workspace. If you have selected a folder that does not exist, the IDE automatically creates a folder for you.

- The Sapphire High-Performance SoC is supported by Efinity RISC-V Embedded Software IDE v2023.2.5 and above only.

# **IDE Launcher from Efinity**

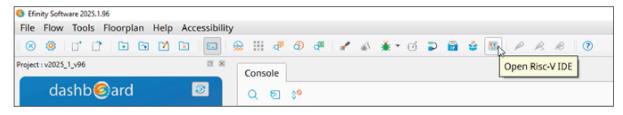

Starting from v2025.1, you can launch the RISC-V IDE from Efinity itself. This feature allows you to easily set-up the workspace and bsp automatically.

**Important:** The button is activated if there is an Efinity project with Sapphire High-Performance SoC instantiated. It greys out if there is no project being opened or no Sapphire High-Performance SoC IP being instantiated.

Figure 6: IDE Launcher Button

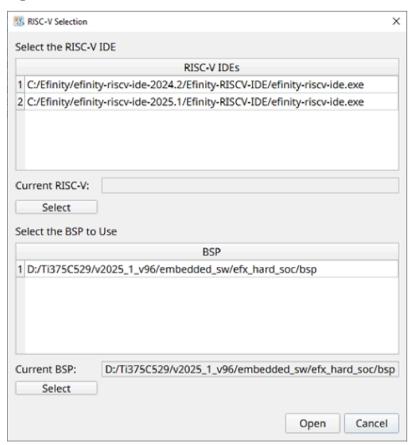

After clicking the button, a dialog pops out. It shows all the installed IDE and BSP, and detects the IDE installed in the same directory as Efinity, e.g., **C:/Efinity/** or **/home/efinity**. If multiple IDEs being detected, you must select only one.

Figure 7: Multiple IDE versions Detected

The IDE Launcher automatically detects the BSP generated after you have instantiated the Soft or Sapphire High-Performance SoC.

Figure 8: BSP Detected

If multiple SoCs are instantiated in the project, e.g., one Sapphire High-Performance SoC and one Sapphire SoC, all the respective BSPs are shown in the BSP dialog box. Accordingly, you need to select only one to proceed.

Figure 9: Multiple BSPs Detected

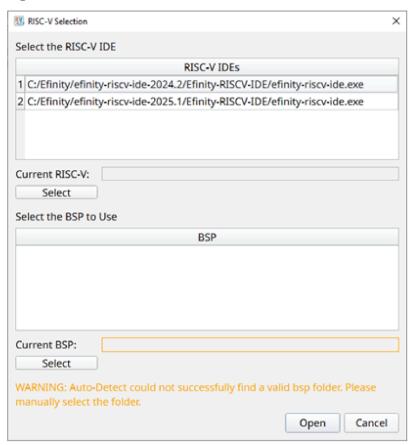

If there is no SoC IP detected, or the BSP is broken, the BSP paths are empty. In this case, you must manually point to the BSP target.

Figure 10: No BSP Detected

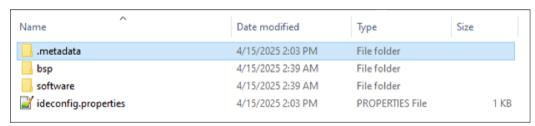

After clicking **Open**, the RISC-V IDE is launched without the workspace selection window. The workspace is created automatically in the **embedded\_sw\efx\_hard\_soc** or **embedded\_sw** \**<soft soc name>**.

There is also an additional file, **ideconfig.properties**, which is created in the same directory. This file contains some information to pass into the IDE.

**Figure 11: Workspace Created Automatically**

## Move Project to Other Location or Machine

You must delete the **folder.metadata** and the file, **ideconfig.properties** before moving the projects to another location or machine. This is to prevent the IDE from using the old workspace after the move to a new location.

# **Optimization Settings**

OpenOCD uses three environment variables, DEBUG, BENCH, and DEBUG OG. It is simplest to set them variables as global environment variables for all projects in your workspace. Then, you can adjust them as needed for individual projects.

Note: When you configure the SoC in the IP Manager, you can choose whether to turn on the debug mode by default or not. When you generate the SoC, the setting is saved in the /embedded\_sw/bsp/efinix/EfxSapphireSoc/include/soc.mk file. If you want to change the debug mode, you can change the setting in the IP Configuration wizard and re-generate the SoC or use the following instructions to add the variables to your project and change them there.

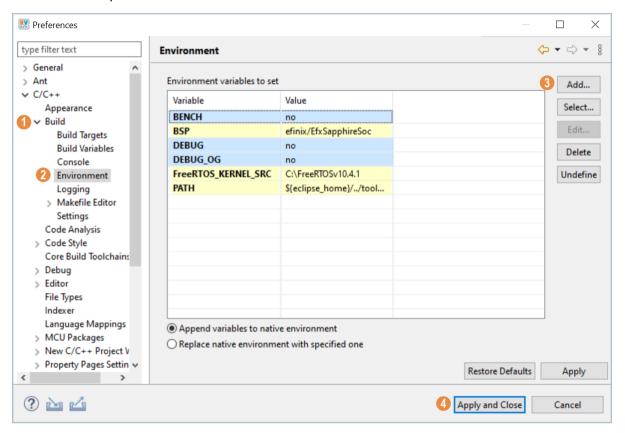

Choose Window > Preferences to open the Preferences window and perform the following

- 1. In the left navigation menu, expand C/C++ > Build.

- 2. Click C/C++ > Build > Environment.

- 3. Click **Add** to add the following environment variables:

- 4. Click Apply and Close.

30

**Table 13: Environment Settings for Preferences Window**

| Variable | Value | Description                                                                                                   |  |

|----------|-------|---------------------------------------------------------------------------------------------------------------|--|

| DEBUG    | no    | Enables or disables debug mode.                                                                               |  |

|          |       | no: Debugging is turned off                                                                                   |  |

|          |       | yes: Debugging is enabled (-g3)                                                                               |  |

|          |       | Note: Setting the DEBUG to no prevents you from debugging step by step in the IDE but saves memory resources. |  |

| DEBUG_OG | no    | Enables or disables optimization during debugging.                                                            |  |

|          |       | Use an uppercase letter O not a zero.                                                                         |  |

|          |       | no: No optimization for debugging (-O0 setting)                                                               |  |

|          |       | yes: Optimization for debugging (-Og setting)                                                                 |  |

| BENCH    | no    | Modify the optimization level when DEBUG is set to <b>no</b> .                                                |  |

|          |       | no: Optimization for size (-Os)                                                                               |  |

|          |       | yes: Optimization for speed (-O3)                                                                             |  |

Alternatively, you may modify the variable through the projects's makefile similar to how it is done for coremark demo project.

```

PROJ_NAME=coremark

STANDALONE = ..

DEBUG=no

BENCH=yes

CFLAGS += -DITERATIONS=2000

SRCS = $(wildcard src/*.c) \

$(wildcard src/*.cpp) \

$(wildcard src/*.s) \

$(standalone)/common/start.S

include ${STANDALONE}/common/bsp.mk

include ${STANDALONE}/common/riscv64-unknown-elf.mk

include ${STANDALONE}/common/standalone.mk

```

Note: For more information on the optimization settings, refer to <a href="https://gcc.gnu.org/onlinedocs/gcc-8.3.0/gcc/Optimize-Options.html">https://gcc.gnu.org/onlinedocs/gcc-8.3.0/gcc/Optimize-Options.html</a>

# Create, Import, and Build a Software Project

#### Contents:

- Create a New Project

- Import Sample Projects

- Build

After you set up your IDE workspace, you are ready to create a new or import an existing project and build it. These instructions walk you through the process using the new project wizard to create a project as well as using the import project wizard to import existing projects and build it.

## Create a New Project

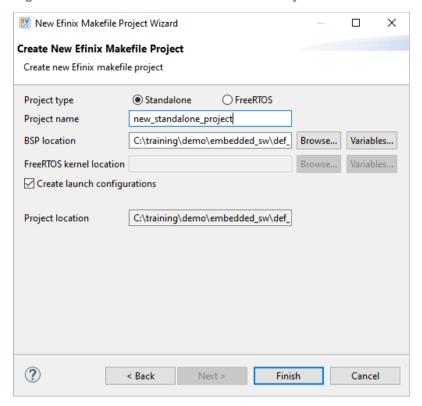

## In the Project Explorer:

- 1. Click Create a Project to open the new project wizard.

- 2. Select the Elitestek Project > Efinix Makefile Project > Next.

#### In the New Efinix Makefile Project Wizard window:

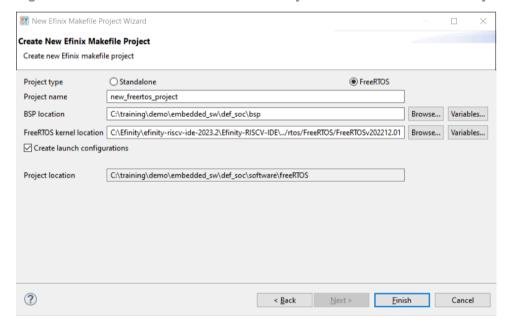

- Select either Standalone or FreeRTOS project type. With this selection, the IDE imports the required header files.

- **4.** Enter your project name. Whitespaces cause error and prevent you to complete the new project creation.

- 5. Click on **Browse...** > **Board Support Package (BSP)**. BSP location is generated by Efinity when you generate the Sapphire High-Performance SoC with the IP Manager. Example BSP location: **C:/<project name>/embedded\_sw/<ip name>/bsp/**.

**Note:** If the Efinity RISC-V Embedded software IDE is launched from the IDE Launcher in Efinity software v2025.1 and later, the BSP location is automatically detected.

- **6.** Select **FreeRTOS**, browse to the **FreeRTOS** kernel location. By default, the kernel location is pointing to the FreeRTOS that comes with package.

- 7. The new project location shows up.

- 8. Click Finish.

Figure 12: Create New Elitestek Makefile Project Wizard for Standalone Project

Figure 13: Create New Elitestek Makefile Project Wizard for FreeRTOS Project

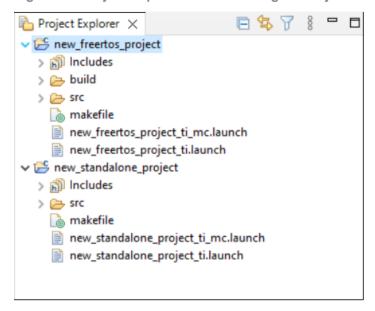

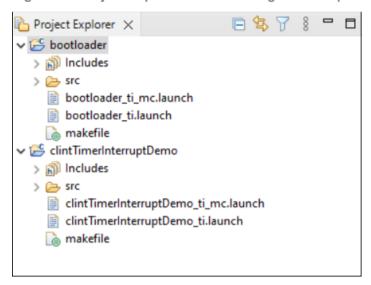

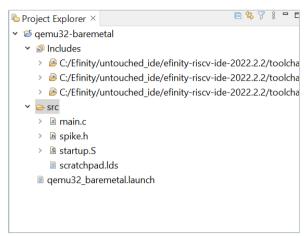

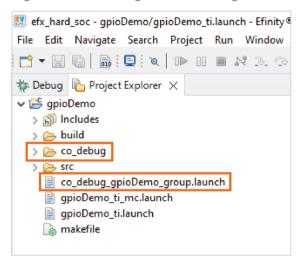

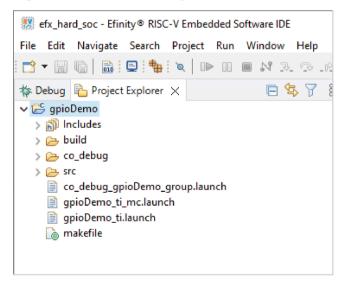

The new projects are updated in the **Project Explorer** pane. All required files are imported automatically. Launch scripts for softTap and ti configurations are generated automatically based on the debug configuration. Both ti.launch and ti\_mc.launch is generated if hard TAP is selected for the Sapphire High-Performance SoC. While softTap.launch and **softTap\_mc.launch** is generated if soft Tap is selected.

33

Figure 14: Project Explorer Pane Showing All Projects Created

You can now browse the source files. To build the project, right-click on the project and select **Clean Project > Build Project**. The compilation output shows in the **Console** window.

Figure 15: Output Console Showing the Newly Generated Standalone Project Built Successfully

Figure 16: Output Console Showing the Newly Generated FreeRTOS Project Built Successfully

# Import Sample Projects

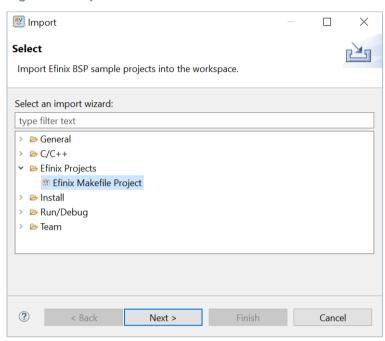

Elitestek provides sample projects to help you get started with Sapphire High-Performance SoC. The sample projects are generated with the Efinity software. The followings steps explain how to import existing projects into the IDE:

- 1. In the Project Explorer, click on Import Projects... to open the Import wizard.

- 2. In the Import wizard, select Elitestek Makefile Project in Elitestek Projects and click Next.

Figure 17: Import Wizard

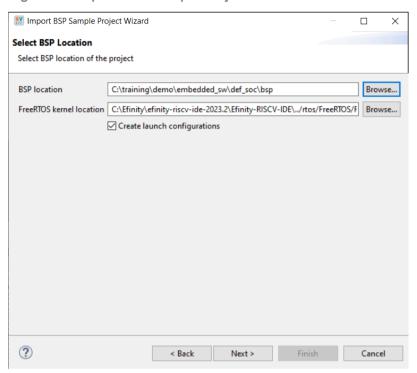

3. In the Import BSP Sample Project Wizard, click Next to browse to the next BSP location box.

**Note:** If the Efinity RISC-V Embedded software IDE is launched from the IDE Launcher in Efinity software v2025.1 and later, the BSP location is automatically detected.

**4.** If you would like to import the FreeRTOS sample projects, browse to the **FreeRTOS kernel location**. Turn on **Create launch configurations** and click **Next**.

Figure 18: Import BSP Sample Project Wizard

Note: FreeRTOS projects is filtered if the FreeRTOS kernel location is not defined.

The next wizard page shows the **Import BSP Sample Project Wizard**, all sample projects are located in the **embedded\_sw/efx\_hard\_soc/software** are shown. Follow these steps:

- 1. Turn on the specific project to import that project.

- **2.** You may turn on the sub-category, for example: Free RTOS, to import all the projects belonging to that particular sub-category.

- **3.** Alternatively, you may click **Select all / Deselect all** to select or deselect all the projects available.

- 4. Click Next.

Import BSP Sample Project Wizard X mport BSP Sample Project Select the BSP sample project(s) to import into the workspace type filter text ✓ ☐ freeRTOS freertosDemo ☐ freertosEchoServerDemo ☐ freertosFatDemo \_\_\_\_ freertoslperfDemo freertosMqttPlainTextDemo → □ application coremark

dhrystone memTest oob bootloader customInstructionDemo fpu fpu fpuDemo ✓ □ gpio gpioDemo √ □ i2c rtcDemo temperatureSensorDemo 🗸 🗌 sdhc fatFSDemo sdhcDemo \_\_ smpDemo ✓ □ spi \_\_\_ spiDemo nestedInterruptDemo userTimerDemo ✓

tsemac ☐ lwiplperfServer uartEchoDemo uartInterruptDemo ✓ □ vexriscv

□ dCacheFlushDemo ☐ iCacheFlushDemo semihostingDemo Select all/Deselect all ? < <u>Back</u> <u>N</u>ext > <u>Finish</u> Cancel

Figure 19: Import BSP Sample Project Wizard - List of Projects

#### Note:

- If you have custom programs that need to be exported to the IDE, you may either copy the programs into existing

folders (FreeRTOS or Standalone) or you can create a folder at the same level as FreeRTOS and Standalone folders.

Automatically, the IDE identifies the folder as a sub-category.

- IDE uses makefile to identify if the folder is considered a project. Ensure that you have a valid makefile for your custom project.

The selected sample projects are imported into the listed workspace in the **Project Explorer** pane.

Figure 20: Project Explorer Pane showing all the Imported Projects

You can now browse the source files. To build the project, right-click the project name and select **Clean Project > Build Project**. The compilation output shows up in the **Console** window.

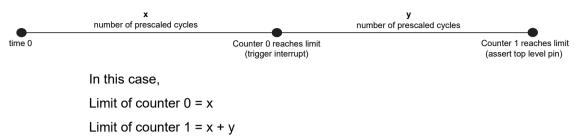

Figure 21: Output Console showing the apb3Demo Standalone Project Built Successfully

### Build

Choose **Project** > **Build Project** or click the Build Project toolbar button. Alternatively, right-click the project name in **Project Explorer** > **Build Project**.

Elitestek recommends cleaning your project before building to ensure all files are compiled. To clean project, right-click on the project in **Project Explorer > Clean Project**.

The makefile builds the project and generates these files in the build directory:

- <project name>.asm—Assembly language file for the firmware.

- <project name>.bin—Firmware binary file. Download this file to the flash device on your board using OpenOCD. When you turn the board on, the SoC loads the application into the RISC-V processor and executes it.

- <project name>.elf—Executable and linkable format. Use this file when debugging with the OpenOCD debugger.

- project name>.hex—Hex file for the firmware. (Do not use it to program the FPGA.)

- <project name>.map—Contains the SoC address map.

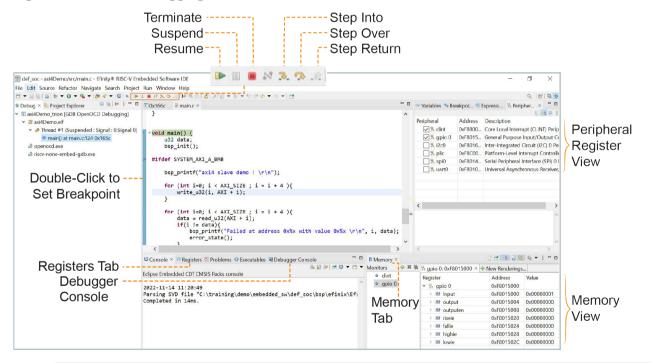

# Debug with the OpenOCD Debugger

#### Contents:

- Launch the Debug Script

- Debug

- Debug Multiple Cores

- Peripheral Register View

- CSR Register View

- FreeRTOS View

- QEMU Emulator

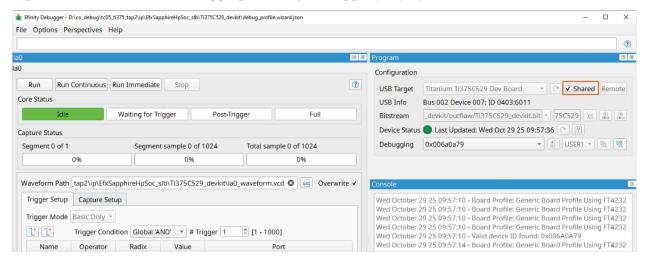

With the development board programmed and the software built, you are ready to configure the OpenOCD debugger and perform debugging. These instructions use the **gpioDemo** example to explain the steps required.

## Launch the Debug Script

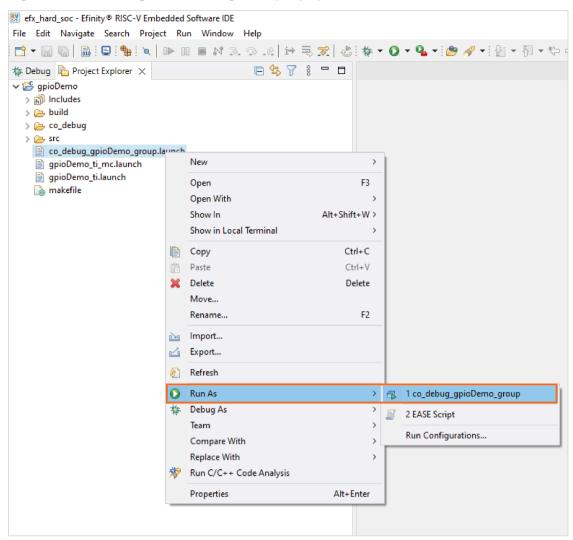

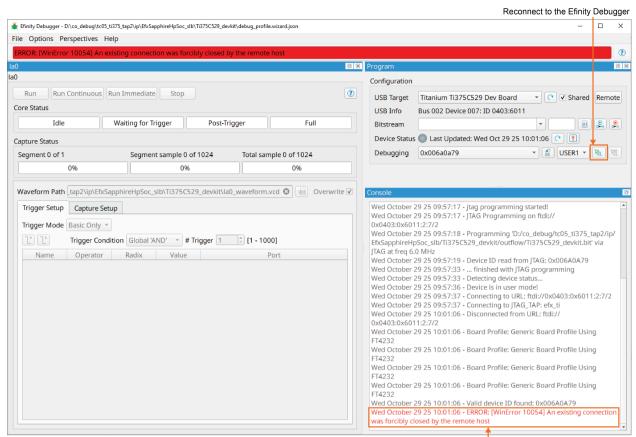

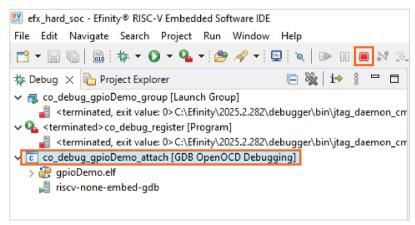

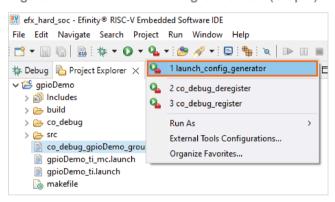

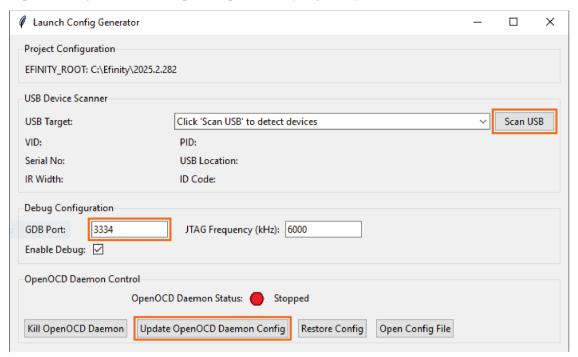

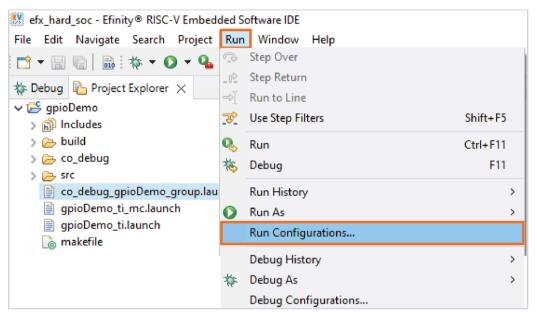

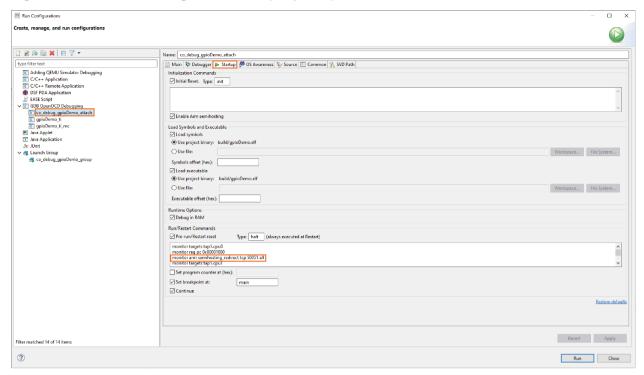

With the Efinity software v2022.2 and higher, debugging scripts are available for each software example in the <code>/embedded\_sw/efx\_hard\_soc/software/</code> directory and are imported into your project when you create a new project or importing existing project into the workspace. You can use these scripts to launch the debug mode.

**Table 14: Debug Configurations**